## ACM32H5xx 用户手册

基于 ARM Star-MC1 内核的 32 位微控制器

版本: V1.5

日期: 2025-3-31

## 目录

| 目录                                                 | 2  |

|----------------------------------------------------|----|

| 1. 文档约定                                            | 45 |

| 1.1. 基本信息                                          | 45 |

| 1.2. 寄存器属性缩写表                                      | 45 |

| 1.3. 术语                                            | 45 |

| 2. 存储器及系统架构 (SYSCFG)                               | 46 |

| 2.1. 内核处理器                                         | 46 |

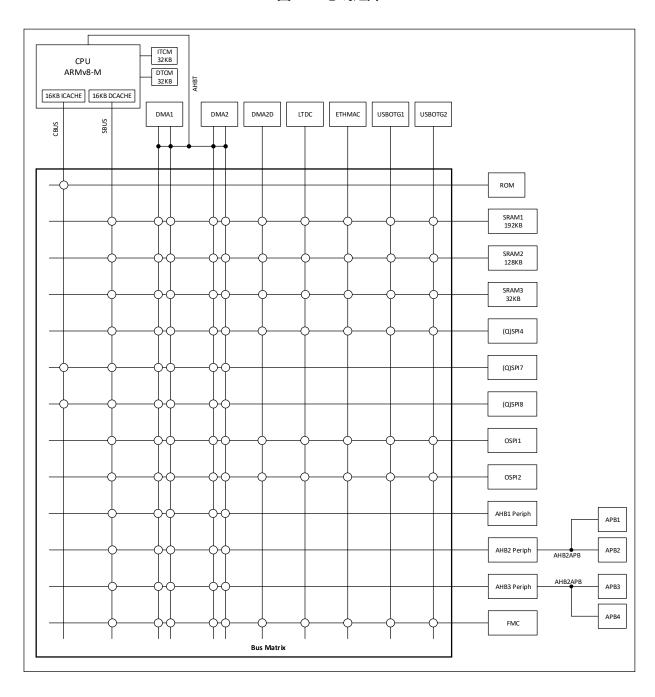

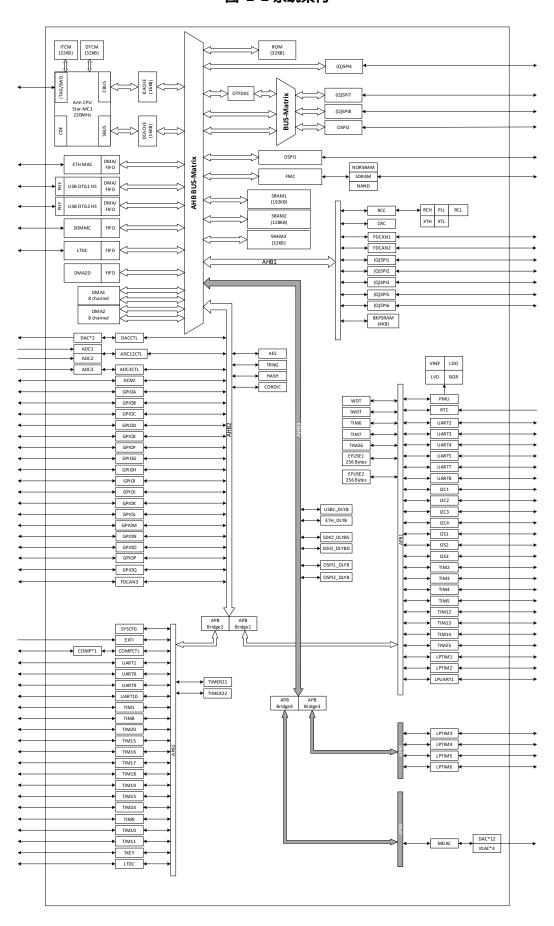

| 2.2. 系统架构                                          | 46 |

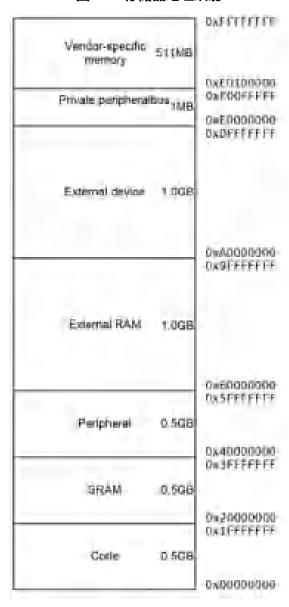

| 2.3. 存储器映射                                         | 50 |

| 2.3.1. SRAM                                        | 58 |

| 2.3.2. ITCM 和 DTCM                                 | 58 |

| 2.3.3. EFUSE                                       | 60 |

| 2.3.4. 内部叠封 SPI-FLASH                              | 60 |

| 2.3.5. 内部叠封 OSPI-PSRAM                             | 60 |

| 2.3.6. 内部叠封 SDRAM                                  | 60 |

| 2.4. 启动配置                                          | 60 |

| 2.5. 设备唯一序列号                                       | 62 |

| 2.6. 系统配置寄存器 (SYSCFG)                              | 62 |

| 2.6.1. 寄存器列表                                       | 62 |

| 2.6.2. 系统控制寄存器(SYSCFG_SYSCR: 00h)                  | 63 |

| 2.6.3. 工作模式寄存器(SYSCFG_WMR: 04h)                    | 65 |

| 2.6.4. 版本寄存器(SYSCFG_VER: 08h)                      | 65 |

| 2.6.5. USBPHY 配置寄存器(SYSCFG_PHYCFG: 10h)            | 65 |

| 2.6.6. SRAM ECC 中断寄存器(SYSCFG_RAMECCIR: 18h)        | 66 |

| 2.6.7. SRAM ECC 状态寄存器(SYSCFG_RAMECCSR: 1Ch)        | 66 |

| 2.6.8. SRAM ECC 中断清除寄存器(SYSCFG_RAMECCICR: 20h)     | 67 |

| 2.6.9. GPIO 5V 输出控制寄存器 1 (SYSCFG_GPIO5VOCR1: 24h)  | 68 |

| 2.6.10. GPIO 5V 输出控制寄存器 2 (SYSCFG_GPIO5VOCR2: 28h) | 71 |

| 3. 电源管理单元 (PMU)                                    | 73 |

| 3.1. PMU 主要特性                                      | 73 |

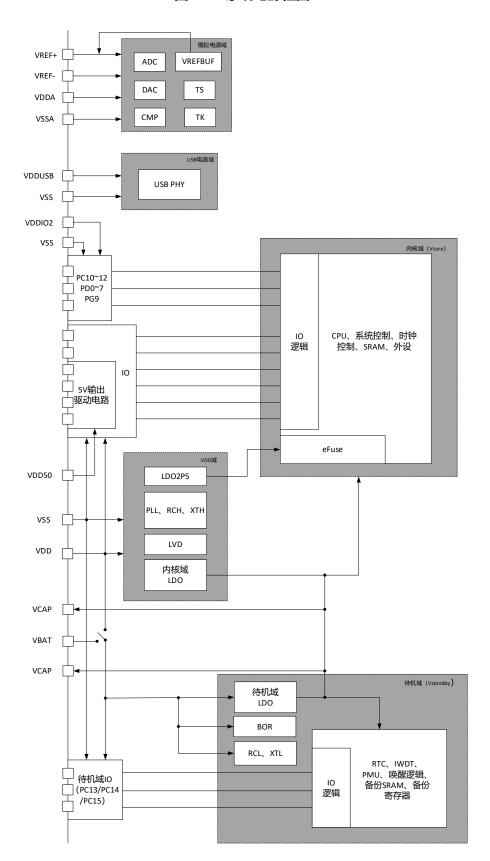

| 3.2. 供电电源                                          | 73 |

| 3.2.1. VDD 电源域                                     | 75 |

| 3.2.2. 模拟电源域                                       | 76 |

| 3.2.3. USB 电源域                                     | 76 |

| 3.2.4. 内核域                                         | 76 |

| 3.2.5. 待机域                                    | 76       |

|-----------------------------------------------|----------|

| 3.2.6. EFUSE 稳压器                              | 77       |

| 3.3. 电源监控                                     | 77       |

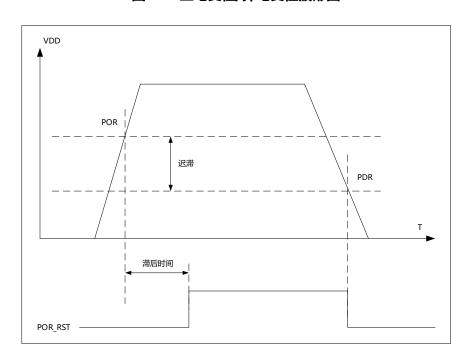

| 3.3.1. 上电复位(POR)/掉电复位(PDR)                    | 77       |

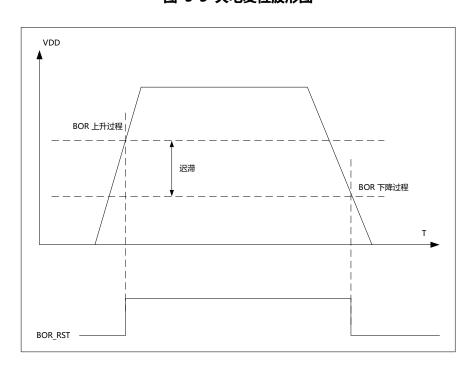

| 3.3.2. 欠压复位(BOR)                              | 78       |

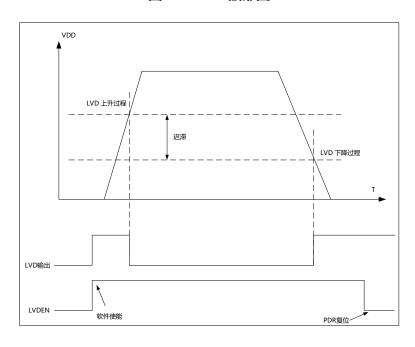

| 3.3.3. 电压检测模块(LVD)                            | 78       |

| 3.4. 低功耗模式                                    | 79       |

| 3.4.1. SLEEP                                  | 79       |

| 3.4.2. STOP                                   | 80       |

| 3.4.3. STANDBY                                | 80       |

| 3.4.4. 低功耗模式下各模块工作状态                          | 81       |

| 3.5. PMU 寄存器描述                                | 82       |

| 3.5.1. 寄存器列表                                  | 82       |

| 3.5.2. PMU 控制寄存器 0(PMU_CTRL0: 00h)            | 82       |

| 3.5.3. PMU 控制寄存器 1(PMU_CTRL1: 04h)            | 83       |

| 3.5.4. 电源控制寄存器 2(PMU_CTRL2: 08h)              | 84       |

| 3.5.5. 电源控制寄存器 3 (PMU_CTRL3: 0Ch)             | 85       |

| 3.5.6. PMU 状态寄存器(PMU_SR: 10h)                 | 85       |

| 3.5.7. PMU 状态清除寄存器(PMU_STCLR: 14h)            | 86       |

| 3.5.8. STANDBY 域 IO 复用寄存器(PMU_IOSEL: 18h)     | 87       |

| 3.5.9. ANATEST 选择寄存器(TEST_ANATEST_SR: C0h) (客 | :户不开放)88 |

| 3.5.10. LDO 校准寄存器(TEST_LDOCAL: C4h) (客户不开放    | z)89     |

| 3.5.11. LDO 测试控制寄存器(TEST_LDOCR: C8h) (客户不)    | 干放)89    |

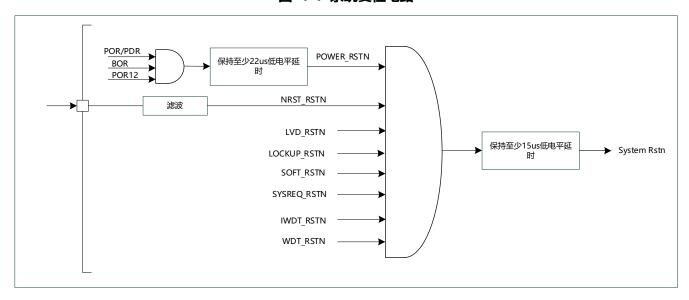

| 4. 复位和时钟控制(RCC)                               | 90       |

| 4.1. 复位                                       | 90       |

| 4.1.1. 电源复位                                   | 90       |

| 4.1.2. 系统复位                                   | 90       |

| 4.1.3. 待机域复位                                  | 91       |

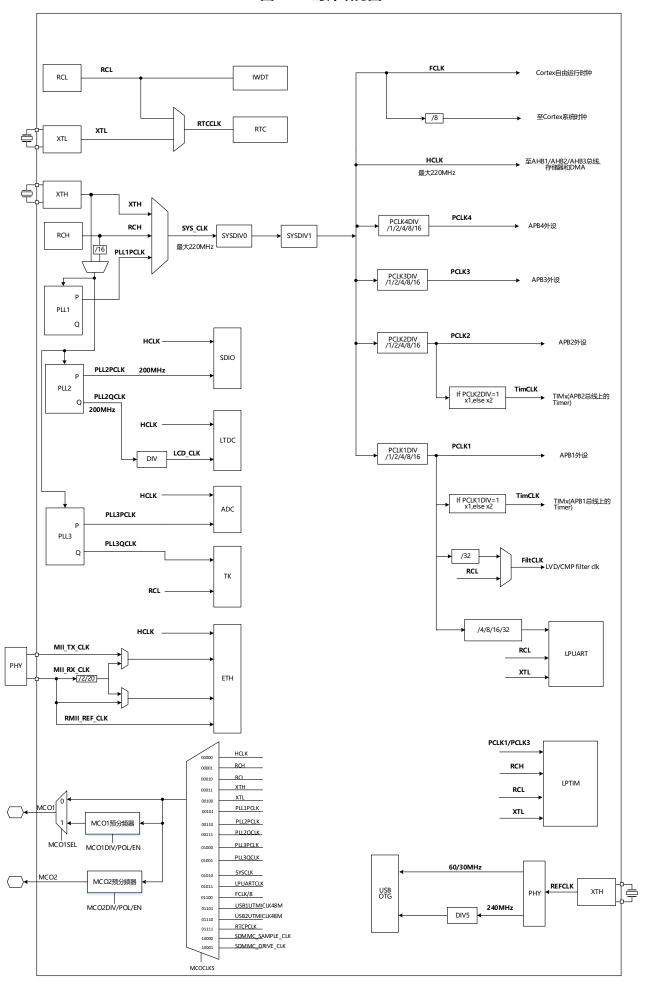

| 4.2. 时钟                                       | 91       |

| 4.2.1. RCH 时钟                                 | 94       |

| 4.2.2. RCL 时钟                                 | 94       |

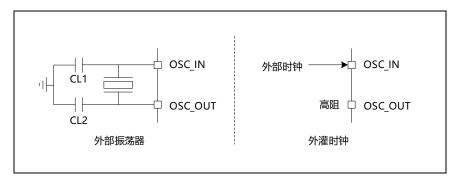

| 4.2.3. XTH 时钟                                 | 95       |

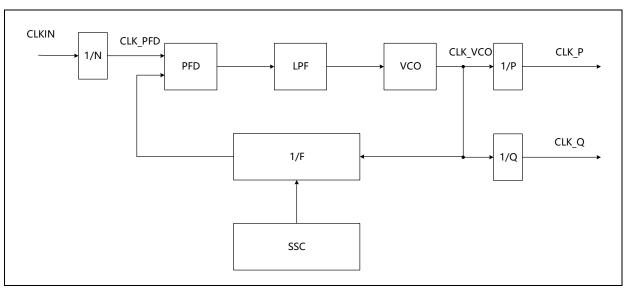

| 4.2.4. XTL 时钟                                 | 95       |

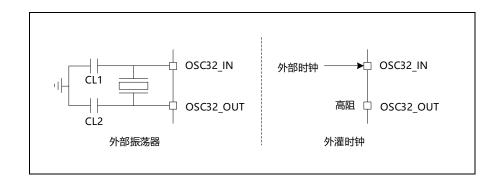

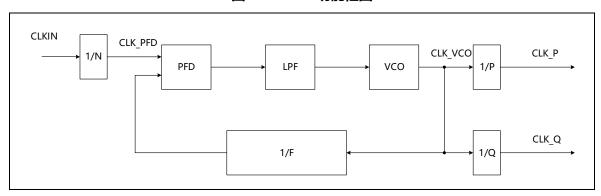

| 4.2.5. PLL 时钟                                 | 96       |

| 4.2.6. 系统时钟                                   | 98       |

| 4.2.7. 时钟安全系统                                 | 99       |

| 4.2.8. RTC 时钟                                 | 99       |

| 4.2.9. 看门狗时钟                                    | 99  |

|-------------------------------------------------|-----|

| 4.2.10. 时钟输出                                    | 99  |

| 4.3. RCC 寄存器描述                                  | 100 |

| 4.3.1. 寄存器列表                                    | 100 |

| 4.3.2. 复位控制寄存器(RCC_RCR: 00h)                    | 101 |

| 4.3.3. 复位源状态寄存器(RCC_RSR: 04h)                   | 101 |

| 4.3.4. AHB1 外设模块复位控制寄存器(RCC_AHB1RSTR: 08h)      | 102 |

| 4.3.5. AHB2 外设模块复位控制寄存器(RCC_AHB2RSTR: 0Ch)      | 104 |

| 4.3.6. AHB3 外设模块复位控制寄存器(RCC_AHB3RSTR: 10h)      | 106 |

| 4.3.7. APB1 外设模块复位控制寄存器 1(RCC_APB1RSTR1: 14h)   | 107 |

| 4.3.8. APB1 外设模块复位控制寄存器 2(RCC_APB1RSTR2: 18h)   | 109 |

| 4.3.9. APB2 外设模块复位控制寄存器(RCC_APB2RSTR: 1Ch)      | 110 |

| 4.3.10. APB3 外设模块复位控制寄存器(RCC_APB3RSTR: 20h)     | 112 |

| 4.3.11. APB4 外设模块复位控制寄存器(RCC_APB4RSTR: 24h)     | 113 |

| 4.3.12. 时钟控制寄存器 1(RCC_CCR1: 28h)                | 114 |

| 4.3.13. 时钟控制寄存器 2(RCC_CCR2: 2Ch)                | 115 |

| 4.3.14. 外设模块时钟配置寄存器(RCC_PERCFGR: 30h)           |     |

| 4.3.15. 时钟中断寄存器(RCC_CIR: 34h)                   | 118 |

| 4.3.16. AHB1 外设模块时钟使能寄存器(RCC_AHB1CKENR: 38h)    | 121 |

| 4.3.17. AHB2 外设模块时钟使能寄存器(RCC_AHB2CKENR: 3Ch)    | 123 |

| 4.3.18. AHB3 外设模块时钟使能寄存器(RCC_AHB3CKENR: 40h)    | 126 |

| 4.3.19. APB1 外设模块时钟使能寄存器 1(RCC_APB1CKENR1: 44h) | 127 |

| 4.3.20. APB1 外设模块时钟使能寄存器 2(RCC_APB1CKENR2: 48h) | 129 |

| 4.3.21. APB2 外设模块时钟使能寄存器(RCC_APB2CKENR: 4Ch)    | 130 |

| 4.3.22. APB3 外设模块时钟使能寄存器(RCC_APB3CKENR: 50h)    | 132 |

| 4.3.23. APB4 外设模块时钟使能寄存器(RCC_APB4CKENR: 54h)    | 133 |

| 4.3.24. RCH 模块控制寄存器(RCC_RCHCR: 58h)             | 134 |

| 4.3.25. XTHCR 模块控制寄存器(RCC_XTHCR: 5Ch)           | 135 |

| 4.3.26. PLL1 模块控制寄存器(RCC_PLL1CR: 60h)           | 136 |

| 4.3.27. PLL1 模块配置寄存器(RCC_PLL1CFR: 64h)          | 137 |

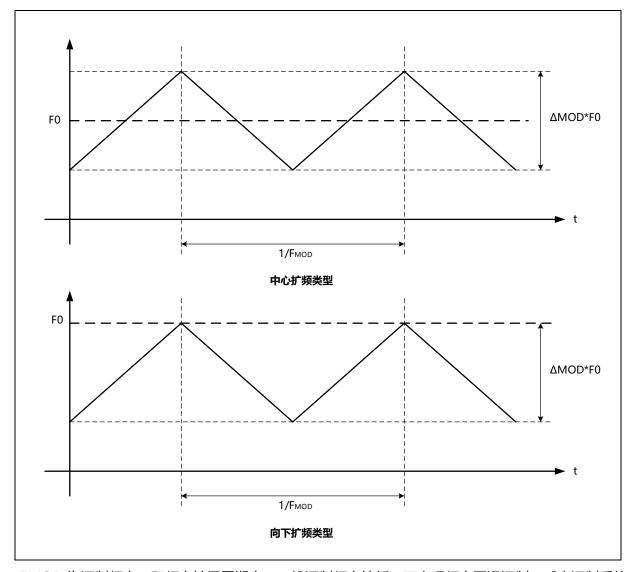

| 4.3.28. PLL1 模块扩频控制寄存器(RCC_PLL1SCR: 68h)        | 138 |

| 4.3.29. PLL2 模块控制寄存器(RCC_PLL2CR: 6Ch)           | 139 |

| 4.3.30. PLL2 模块配置寄存器(RCC_PLL2CFR: 70h)          | 140 |

| 4.3.31. PLL2 模块扩频控制寄存器(RCC_PLL2SCR: 74h)        | 141 |

| 4.3.32. PLL3 模块控制寄存器(RCC_PLL3CR: 78h)           | 142 |

| 4.3.33. PLL3 模块配置寄存器(RCC_PLL3CFR: 7Ch)          | 143 |

| 4.3.34. 时钟输出控制寄存器(RCC_CLKOCR: 84h)              | 144 |

| 4.3.35. 外设专用时钟配置寄存器(RCC_DCKCFG: 88h)         | 145 |

|----------------------------------------------|-----|

| 4.3.36. STANDBY 电源域控制寄存器(RCC_STDBYCTRL: 8Ch) | 145 |

| 5. 嵌套向量中断控制器 (NVIC)                          | 148 |

| 5.1. 概述                                      | 148 |

| 5.2. 主要特性                                    | 148 |

| 5.3. 中断源                                     | 148 |

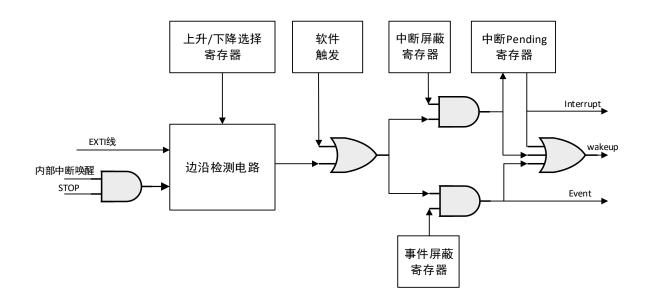

| 6. 外部中断/事件控制器 (EXTI)                         | 154 |

| 6.1. 概述                                      | 154 |

| 6.2. 主要特性                                    | 154 |

| 6.3. 结构框图                                    | 154 |

| 6.4. 触发源                                     | 154 |

| 6.5. 唤醒管理                                    | 156 |

| 6.6. 功能描述                                    | 156 |

| 6.6.1. EXTI 中断                               | 156 |

| 6.6.2. EXTI 中断/事件唤醒                          | 156 |

| 6.7. EXTI 寄存器描述                              | 157 |

| 6.7.1. 寄存器列表                                 | 157 |

| 6.7.2. 中断使能寄存器(IENR1: 00h)                   | 157 |

| 6.7.3. 中断使能寄存器(IENR2: 04h)                   | 157 |

| 6.7.4. 事件使能寄存器(EENR1: 08h)                   | 158 |

| 6.7.5. 事件使能寄存器(EENR2: 0Ch)                   | 158 |

| 6.7.6. 上升沿触发使能寄存器(RTENR1: 10h)               | 158 |

| 6.7.7. 上升沿触发使能寄存器(RTENR2: 14h)               | 158 |

| 6.7.8. 下降沿触发使能寄存器(FTENR1: 18h)               | 159 |

| 6.7.9. 下降沿触发使能寄存器(FTENR2: 1Ch)               | 159 |

| 6.7.10. 软件中断事件寄存器(SWIER1: 20h)               | 159 |

| 6.7.11. 软件中断事件寄存器(SWIER2: 24h)               | 159 |

| 6.7.12. 中断挂起寄存器(PDR1: 28h)                   | 160 |

| 6.7.13. 中断挂起寄存器(PDR2: 2Ch)                   | 160 |

| 6.7.14. 外部中断配置寄存器(1 EXTICR1: 30h)            | 160 |

| 6.7.15. 外部中断配置寄存器(2 EXTICR2: 34h)            | 161 |

| 6.7.16. 外部中断配置寄存器(3 EXTICR3: 38h)            | 162 |

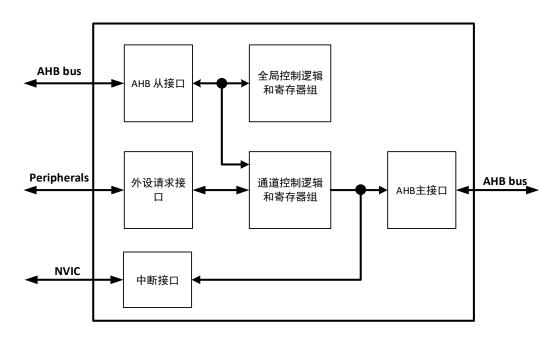

| 7. DMA 控制器 (DMA)                             | 164 |

| 7.1. 概述                                      | 164 |

| 7.2. 主要特性                                    | 164 |

| 7.3. 功能说明                                    | 165 |

| 7.3.1. 框图                                    | 165 |

| 7.3.2. 通道                                                   | 165 |

|-------------------------------------------------------------|-----|

| 7.3.3. 外设请求                                                 | 165 |

| 7.3.4. 仲裁器                                                  | 170 |

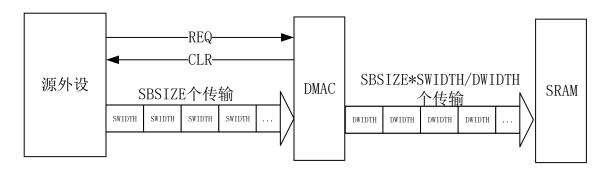

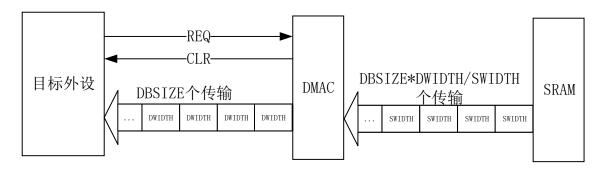

| 7.3.5. 传输位宽                                                 | 170 |

| 7.3.6. 突发传输                                                 | 171 |

| 7.3.7. 源、目标                                                 | 171 |

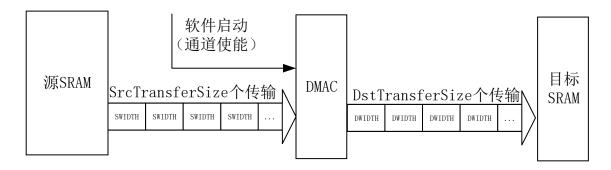

| 7.3.8. 传输模式                                                 | 171 |

| 7.3.9. 指针递增                                                 | 173 |

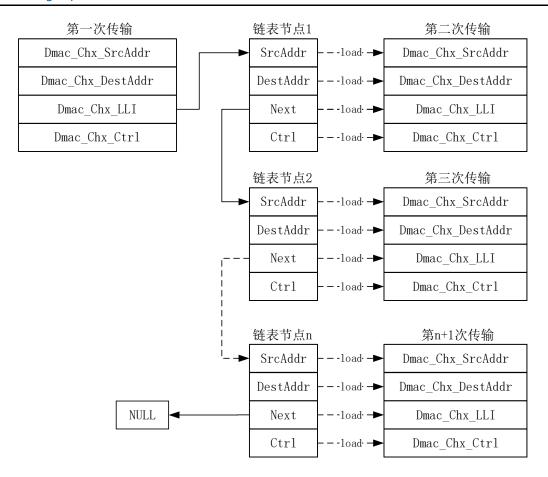

| 7.3.10. 链表模式                                                | 174 |

| 7.3.11. 循环模式                                                | 175 |

| 7.3.12. 双缓冲模式                                               | 175 |

| 7.3.13. 可编程端模式、数据宽度、封装/解封、字节序                               | 175 |

| 7.3.14. 关闭 DMA 通道                                           | 177 |

| 7.3.15. 暂停 DMA 通道                                           | 177 |

| 7.3.16. 中断                                                  | 178 |

| 7.4. 配置流程                                                   | 179 |

| 7.5. DMA 寄存器描述                                              | 179 |

| 7.5.1. 寄存器列表                                                | 179 |

| 7.5.2. 中断状态寄存器(DMA_INT_STATUS: 00h)                         | 180 |

| 7.5.3. 传输完成中断寄存器(DMA_INT_TC_STATUS: 04h)                    | 180 |

| 7.5.4. 传输完成中断清除寄存器(DMA_INT_TC_CLR: 08h)                     | 180 |

| 7.5.5. 传输错误中断寄存器(DMA_INT_ERR_STATUS: 0Ch)                   | 181 |

| 7.5.6. 传输错误中断清除寄存器(DMA_INT_ERR_CLR: 10h)                    | 181 |

| 7.5.7. 传输完成原始中断寄存器(DMA_RAW_INT_TC_STATUS: 14h)              | 181 |

| 7.5.8. 传输错误原始中断寄存器(DMA_RAW_INT_ERR_STATUS: 18h)             | 181 |

| 7.5.9. 通道使能状态寄存器(DMA_EN_CH_STATUS: 1Ch)                     | 182 |

| 7.5.10. DMA 配置寄存器(DMA_CONFIG: 30h)                          | 182 |

| 7.5.11. 源通道 x 地址寄存器(DMA_Cx_SRC_ADDR: 100h+(x*20h), x=0~7)   | 182 |

| 7.5.12. 目标通道 x 地址寄存器(DMA_Cx_DEST_ADDR: 104h+(x*20h), x=0~7) | 182 |

| 7.5.13. 通道 x 链接表寄存器(DMA_Cx_LLI: 108h+(x*20h), x=0~7)        | 183 |

| 7.5.14. 通道 x 控制寄存器(DMA_Cx_CTRL: 10Ch+(x*20h), x=0~7)        | 183 |

| 7.5.15. 通道 x 配置寄存器(DMA_Cx_CONFIG: 110h+(x*20h), x=0~7)      | 184 |

| 一次性可编程存储器(EFUSE)                                            | 186 |

| 8.1. 概述                                                     | 186 |

| 8.2. 主要特性                                                   | 186 |

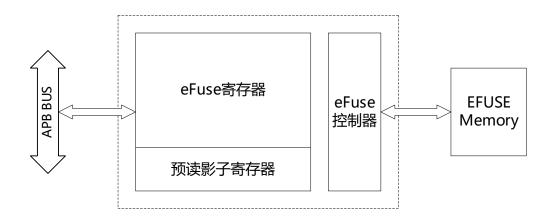

| 8.3. 结构框图                                                   | 186 |

| 8.4. 功能说明                                                   | 186 |

8.

| 8.4.1. 硬件预读                                         | 186 |

|-----------------------------------------------------|-----|

| 8.4.2. 编程模式                                         | 187 |

| 8.4.3. 读取模式                                         | 187 |

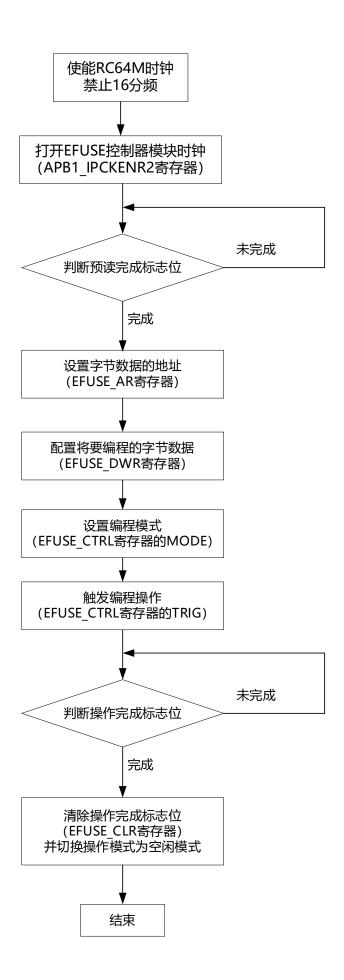

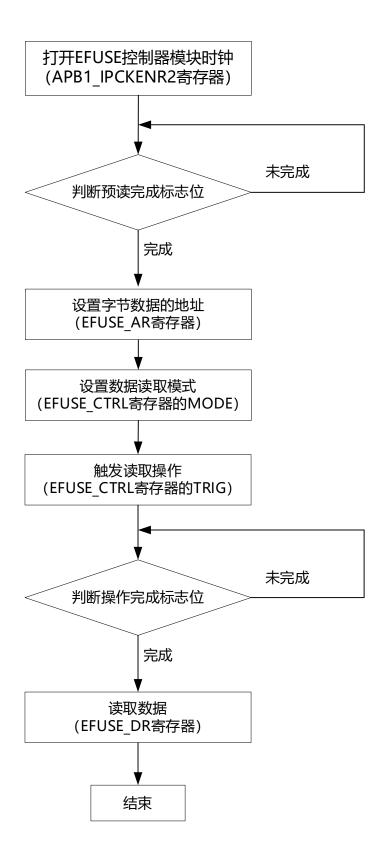

| 8.5. 配置流程                                           | 188 |

| 8.5.1. 编程操作                                         | 188 |

| 8.5.2. 读取操作                                         | 189 |

| 8.6. EFUSE 寄存器描述                                    | 189 |

| 8.6.1. 寄存器列表                                        | 189 |

| 8.6.2. 写保护寄存器(EFUSE_WP: 00h)                        | 190 |

| 8.6.3. 控制寄存器(EFUSE_CTRL: 04h)                       | 190 |

| 8.6.4. 地址寄存器(EFUSE_AR: 0x08)                        | 191 |

| 8.6.5. 字节数据写入寄存器(EFUSE_DWR: 0x0C)                   | 191 |

| 8.6.6. 状态寄存器(EFUSE_SR: 0x10)                        | 191 |

| 8.6.7. 状态清零寄存器(EFUSE_CLR: 0x14)                     | 191 |

| 8.6.8. 数据读取寄存器(EFUSE_DR: 0x18)                      | 192 |

| 8.6.9. 预读数据影子寄存器(读保护 EFUSE_DSDP: 0x1C)              | 192 |

| 8.6.10. 字节编程保护寄存器(EFUSE_BYTEWP: 0x20)               | 192 |

| 8.6.11. 编程参数配置寄存器(EFUSE_PGCFG: 0x24)                | 192 |

| 8.6.12. 预读数据影子寄存器 x(EFUSE_DSRx: 400h+(x*4), x=0~15) | 193 |

| 9. 延迟模块 (DLYB)                                      | 194 |

| 9.1. 概述                                             | 194 |

| 9.2. 主要特性                                           | 194 |

| 9.3. 结构框图                                           | 194 |

| 9.4. 功能描述                                           | 195 |

| 9.4.1. 延迟线长度配置步骤                                    | 195 |

| 9.4.2. 输出时钟相位配置步骤                                   | 196 |

| 9.5. DLYB 寄存器描述                                     | 196 |

| 9.5.1. 寄存器列表                                        | 196 |

| 9.5.2. DLYB 控制寄存器(DLYB_CR: 00h)                     | 196 |

| 9.5.3. DLYB 配置寄存器(DLYB_CFGR: 04h)                   | 197 |

| 10. 通用输入输出口(GPIO)                                   | 198 |

| 10.1. 概述                                            | 198 |

| 10.2. 主要特性                                          | 198 |

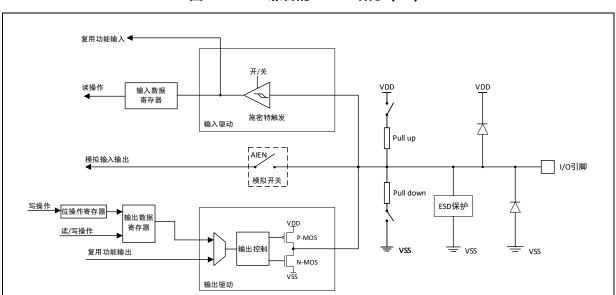

| 10.3. 功能描述                                          | 198 |

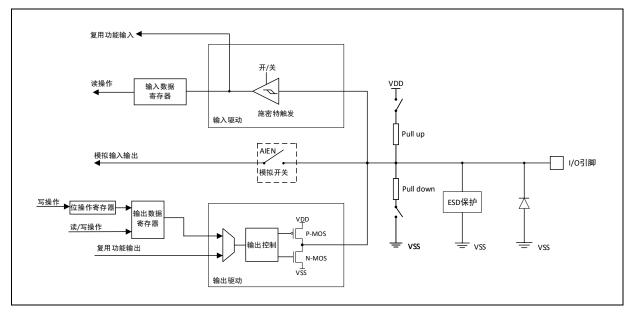

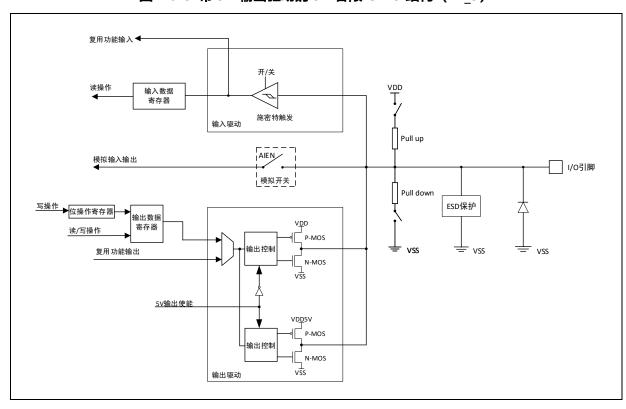

| 10.3.1. 结构框图                                        | 199 |

| 10.3.2. 输入功能                                        | 200 |

| 10.3.3. 输出功能                                        | 200 |

| 10.3.4. 5V 输出驱动                           | 201 |

|-------------------------------------------|-----|

| 10.3.5. 模拟功能                              | 201 |

| 10.3.6. 复用功能                              | 201 |

| 10.3.7. 外部中断/事件线                          | 202 |

| 10.3.8. GPIO 锁定功能                         | 202 |

| 10.4. GPIO 寄存器描述                          | 202 |

| 10.4.1. 寄存器列表                             | 202 |

| 10.4.2. GPIO 模式寄存器(GPIOx_MD: 00h)         | 203 |

| 10.4.3. GPIO 输出类型寄存器(GPIOx_OTYP: 04h)     | 203 |

| 10.4.4. GPIO 上下拉寄存器(GPIOx_PUPD: 08h)      | 204 |

| 10.4.5. GPIO 输入引脚映射寄存器 (GPIOx_IDATA: 0Ch) | 204 |

| 10.4.6. GPIO 输出引脚映射寄存器(GPIOx_ODATA: 10h)  | 204 |

| 10.4.7. GPIO 输出置位/清零寄存器(GPIOx_BSC: 14h)   | 205 |

| 10.4.8. GPIO 复用功能配置寄存器 0(GPIOx_AF0: 18h)  | 205 |

| 10.4.9. GPIO 复用功能配置寄存器 1(GPIOx_AF1: 1Ch)  | 205 |

| 10.4.10. GPIO 驱动能力配置寄存器 0(GPIOx_DS0: 20h) | 205 |

| 10.4.11. GPIO 驱动能力配置寄存器 1(GPIOx_DS1: 24h) | 206 |

| 10.4.12. GPIO 施密特使能寄存器(GPIOx_SMIT: 28h)   | 207 |

| 10.4.13. GPIO 配置锁定寄存器(GPIOx_LOCK: 2Ch)    | 207 |

| 10.4.14. GPIO 模拟开关配置寄存器(GPIOx_AIEN: 30h)  | 208 |

| 11. 定时器的分类                                | 209 |

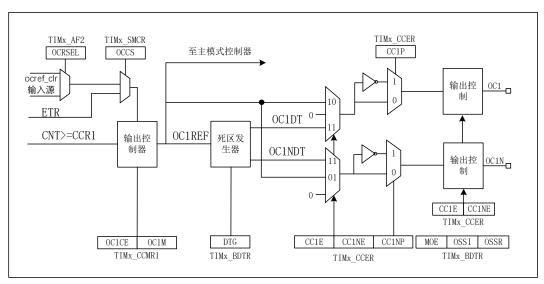

| 12. 高级定时器(TIM1/8/20)                      | 210 |

| 12.1. 概述                                  | 210 |

| 12.2. 主要特性                                | 210 |

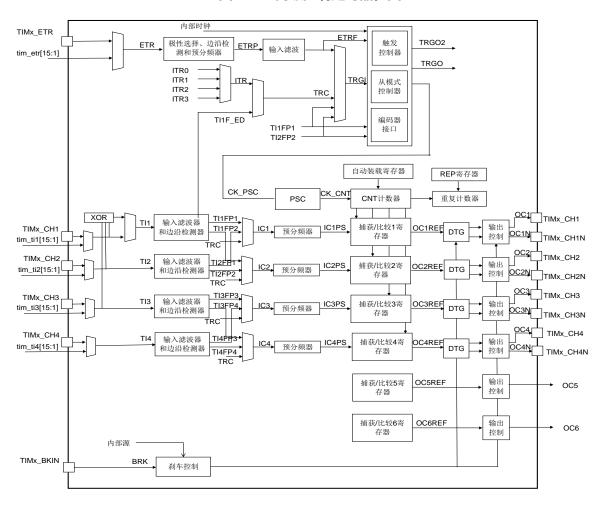

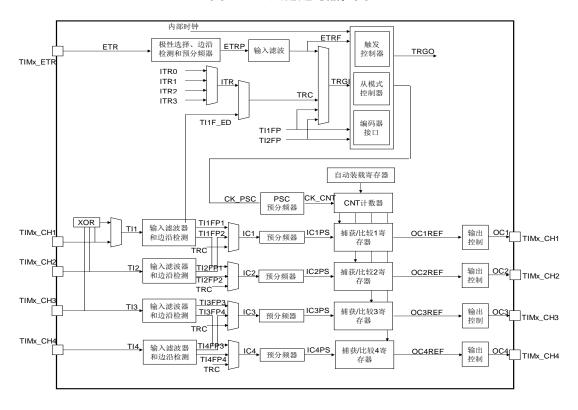

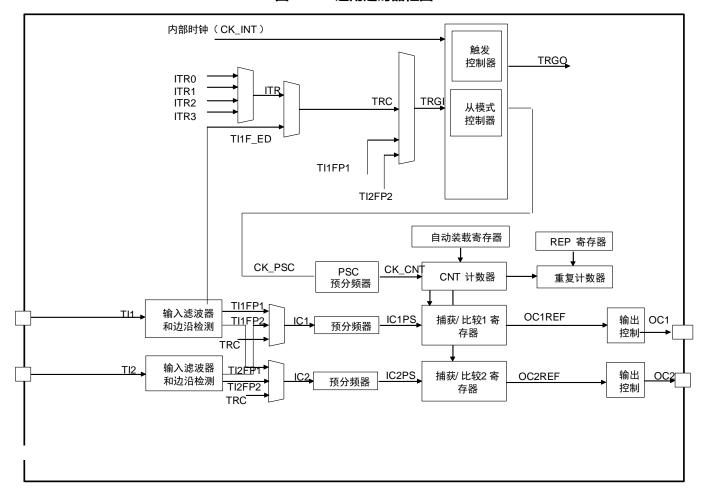

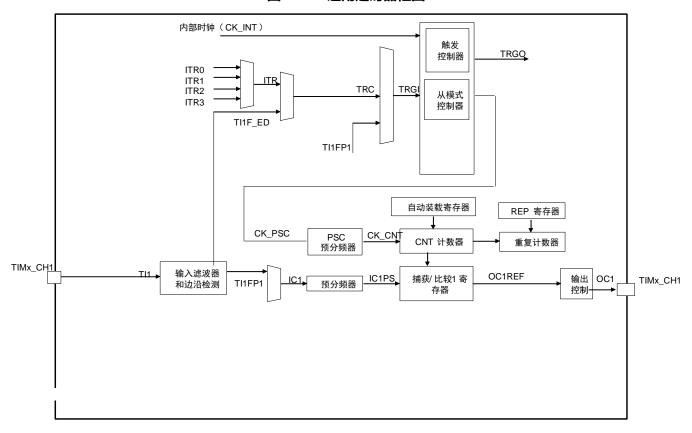

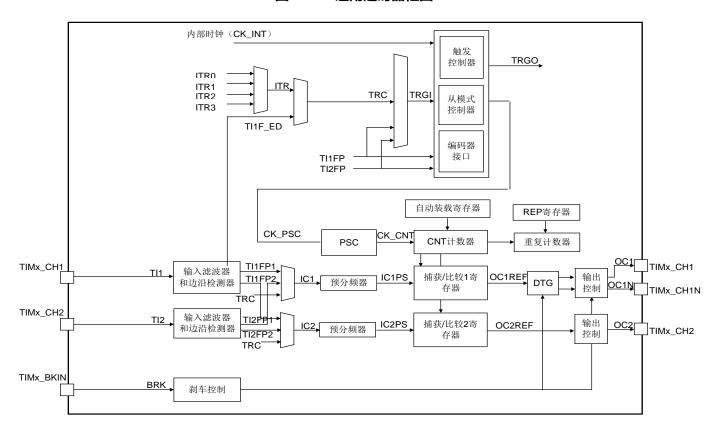

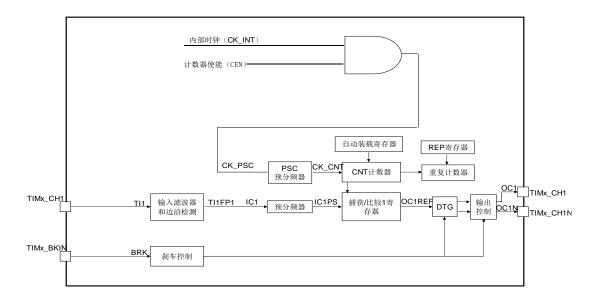

| 12.3. 结构框图                                | 211 |

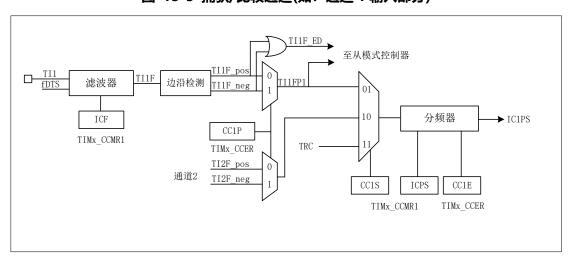

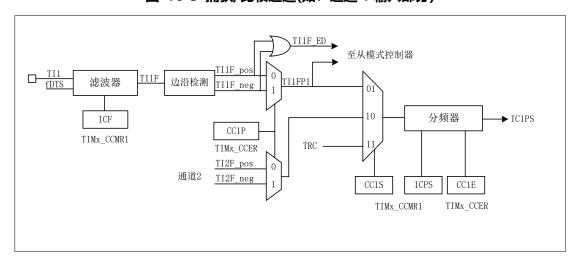

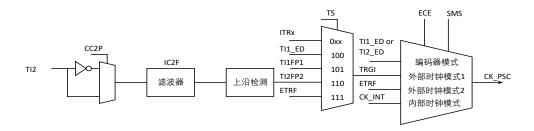

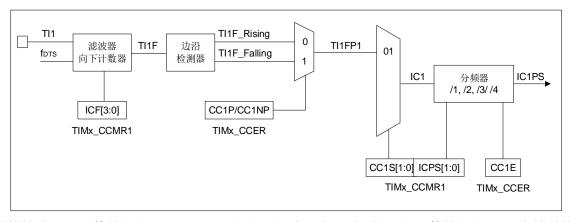

| 12.4. TIMx 输入映射                           | 211 |

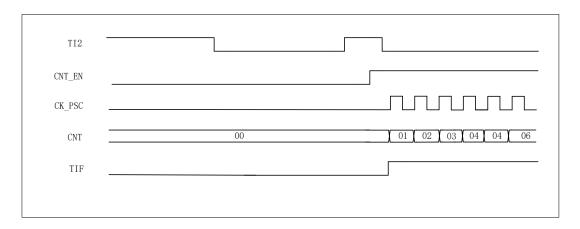

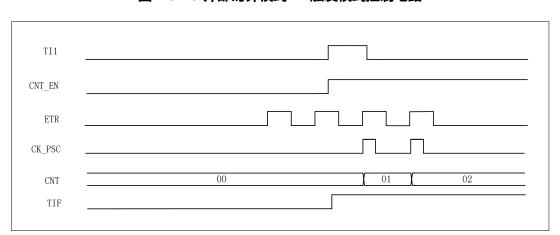

| 12.5. 功能描述                                | 213 |

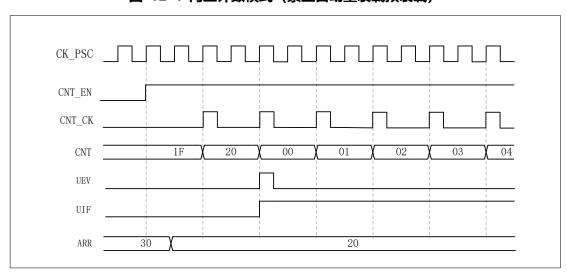

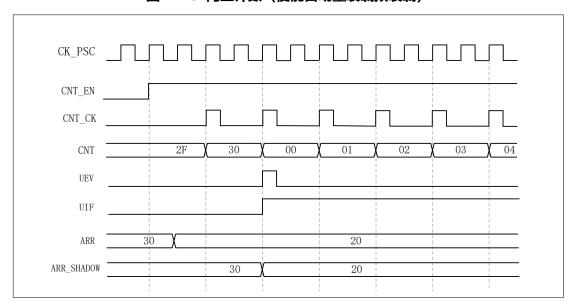

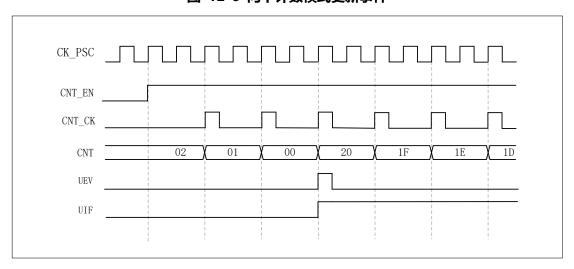

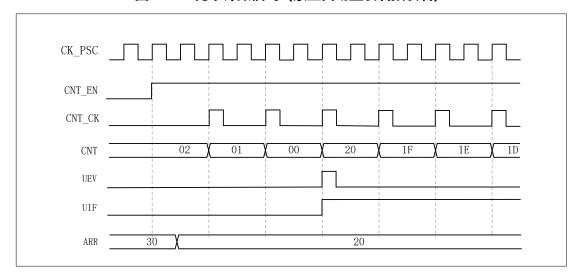

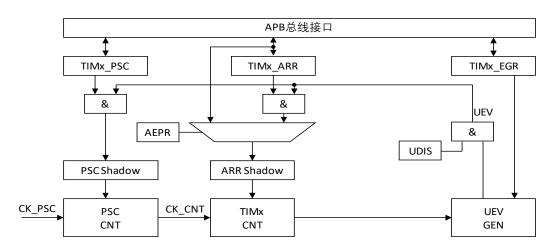

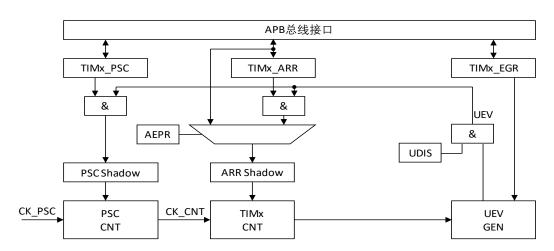

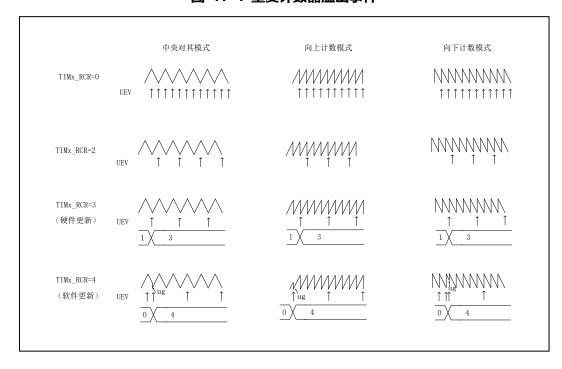

| 12.5.1. 计数单元                              | 213 |

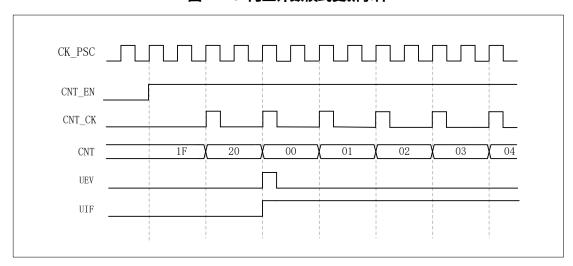

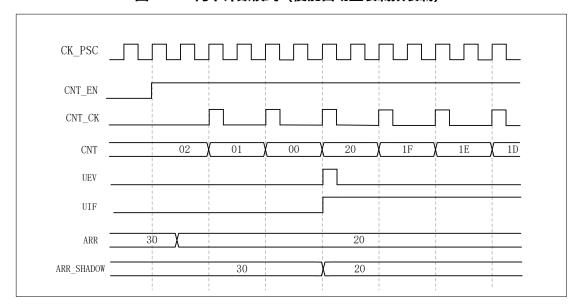

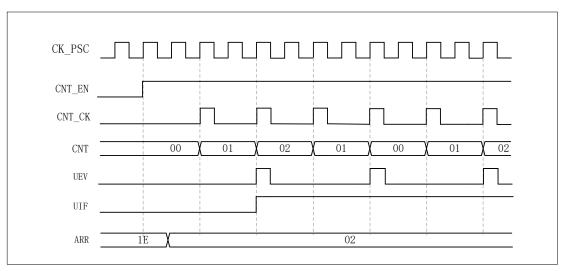

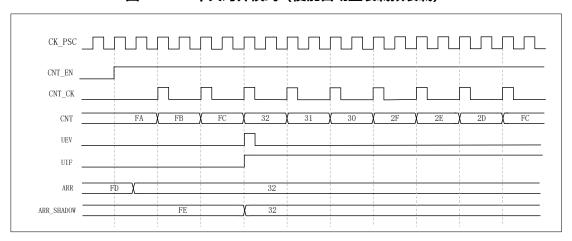

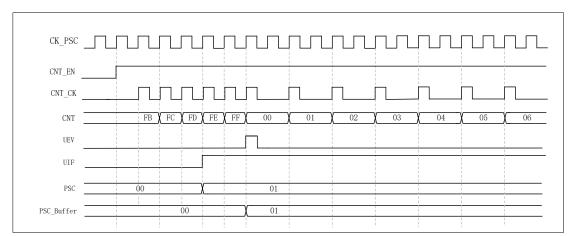

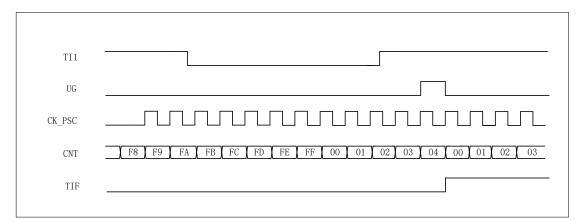

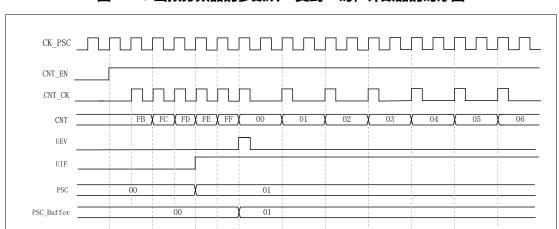

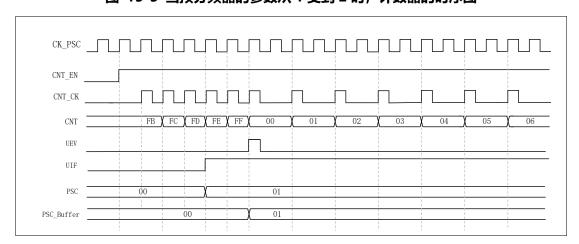

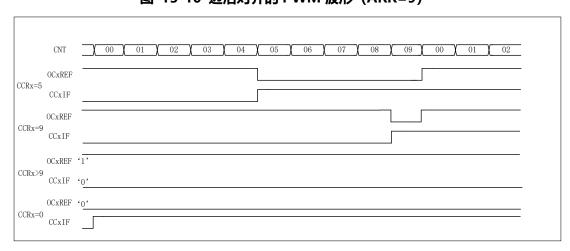

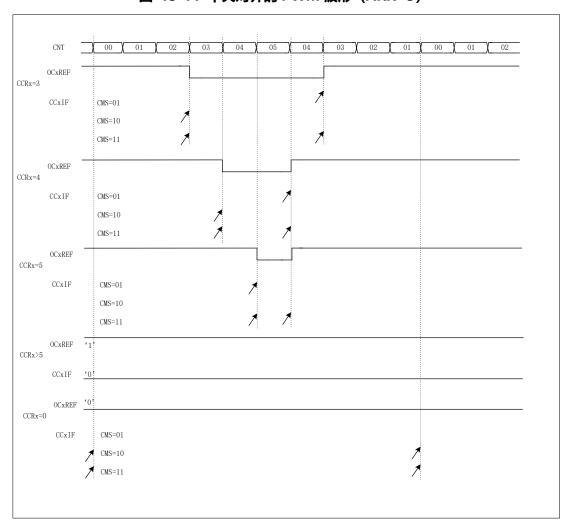

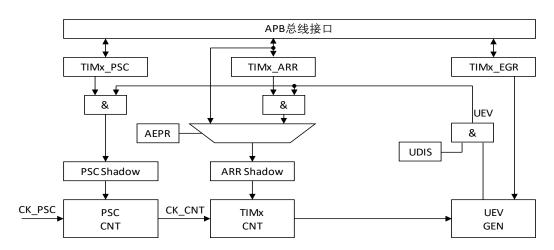

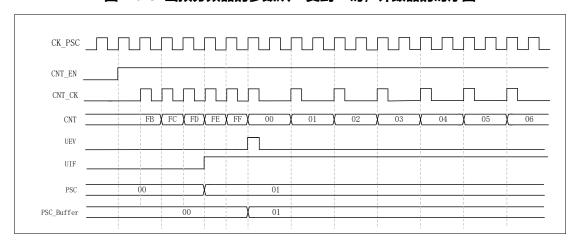

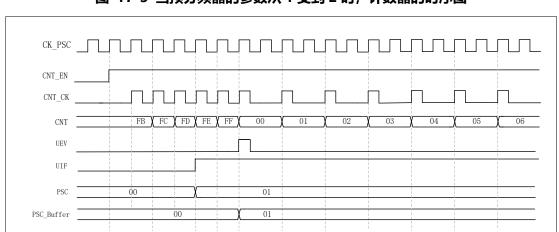

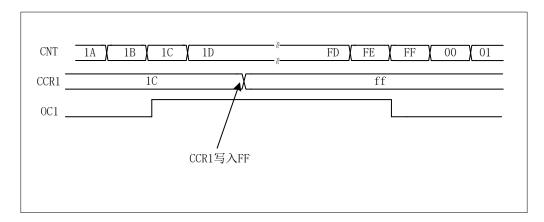

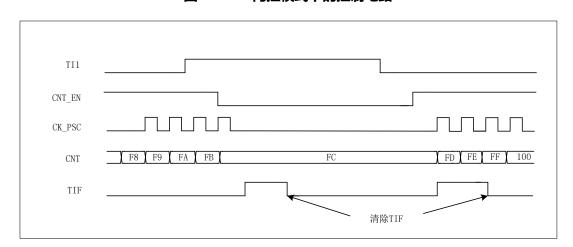

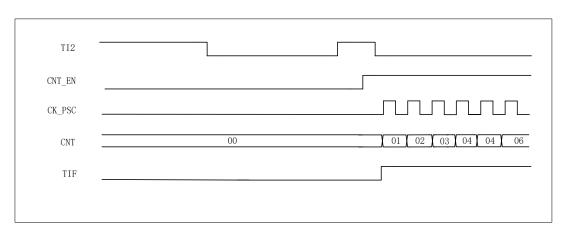

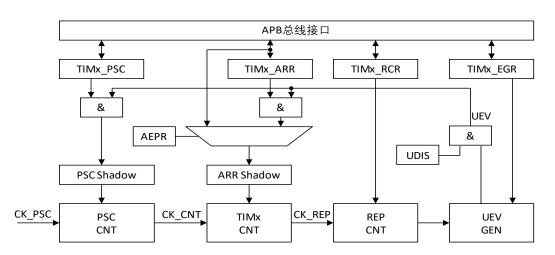

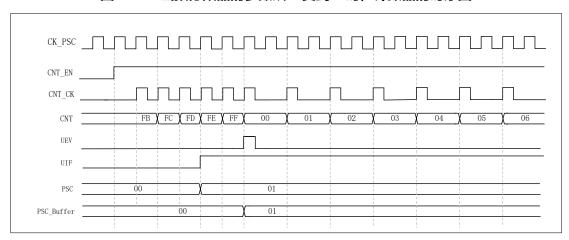

| 12.5.2. 预分频器                              | 218 |

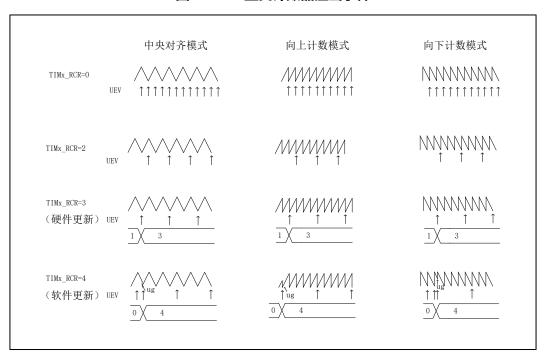

| 12.5.3. 重复计数器                             | 218 |

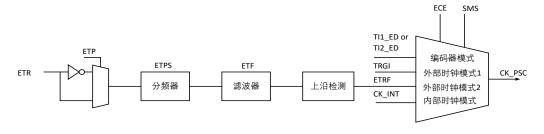

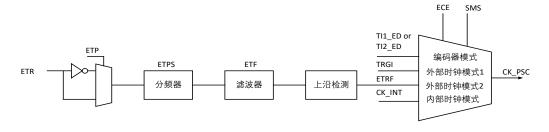

| 12.5.4. 外部触发输入                            | 219 |

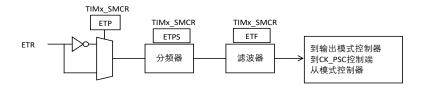

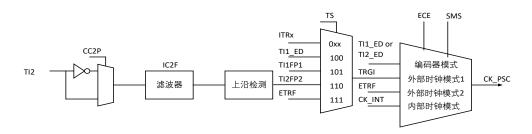

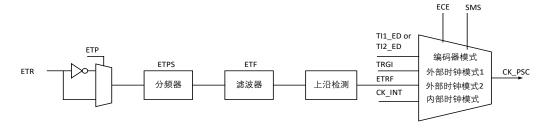

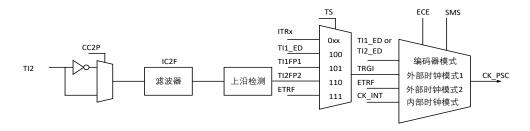

| 12.5.5. 时钟源选择                             | 219 |

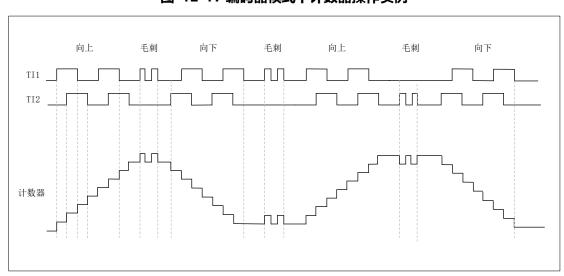

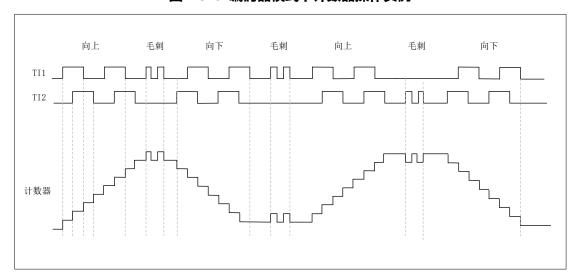

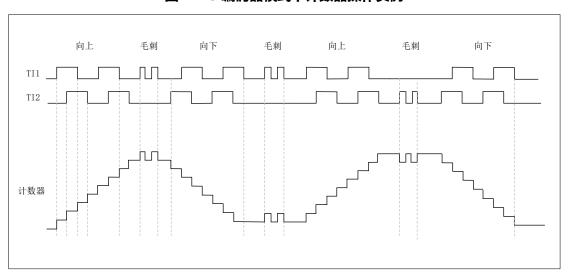

| 12.5.6. 编码器模式                             | 220 |

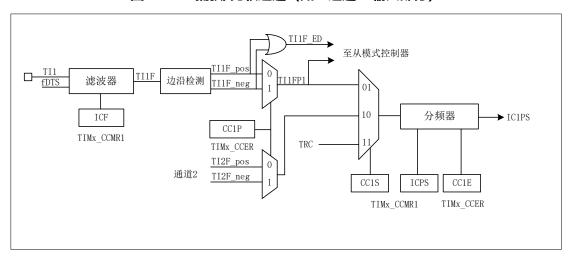

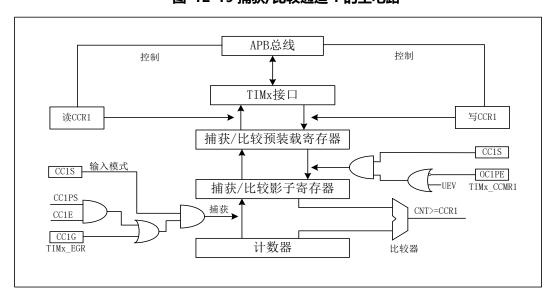

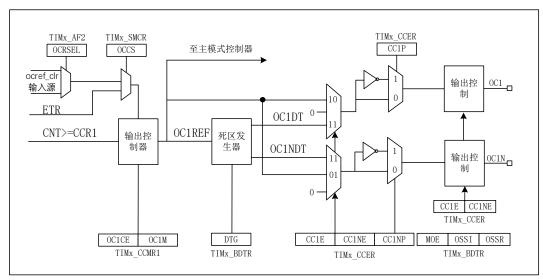

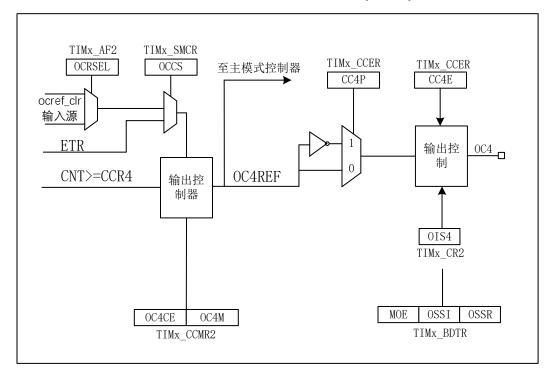

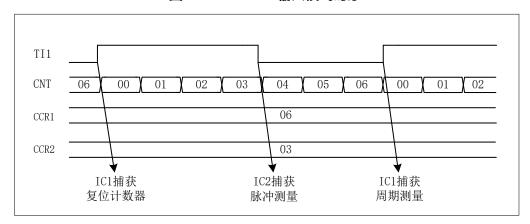

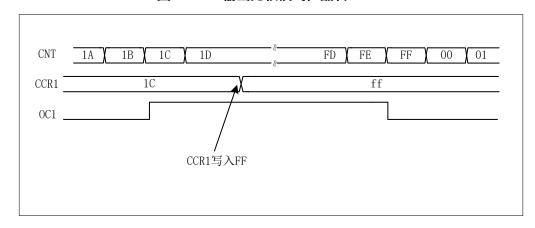

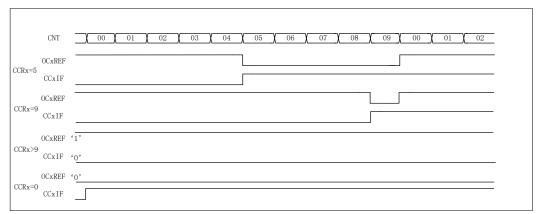

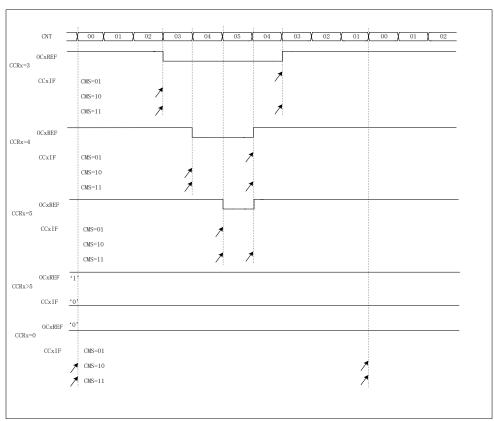

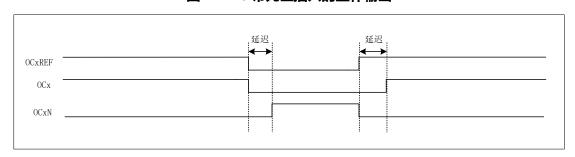

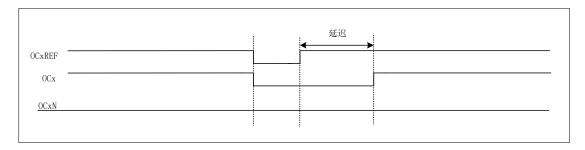

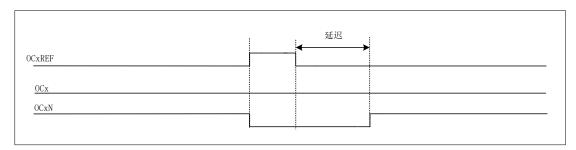

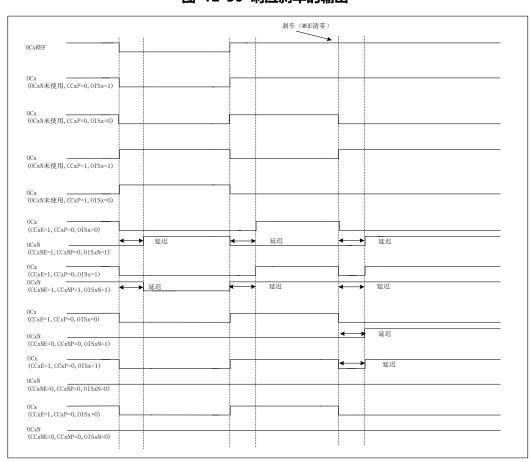

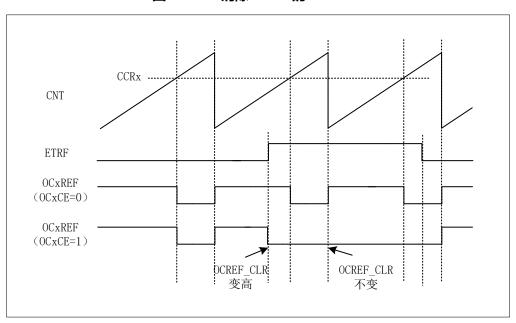

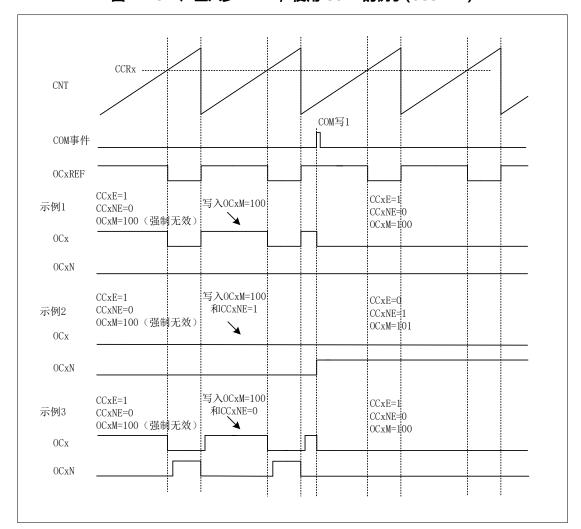

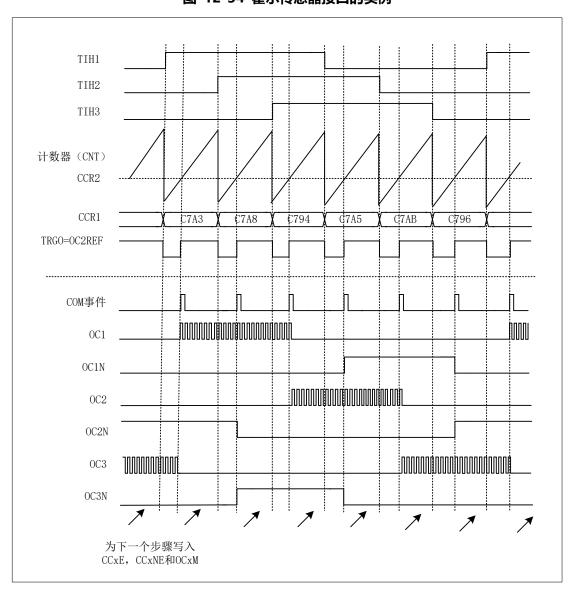

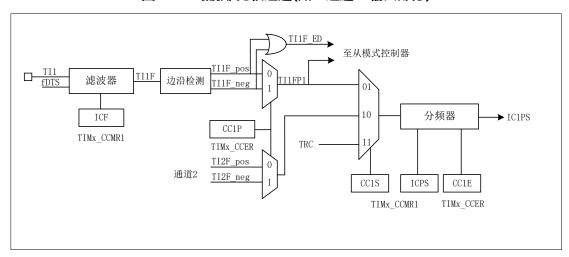

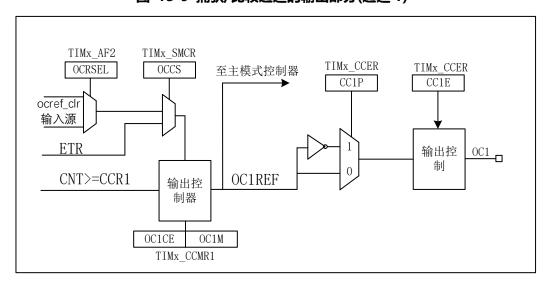

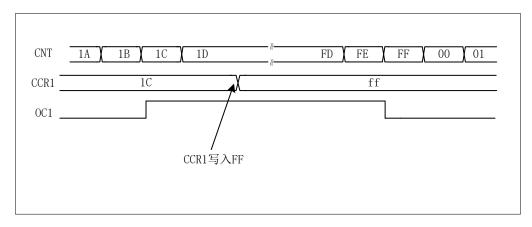

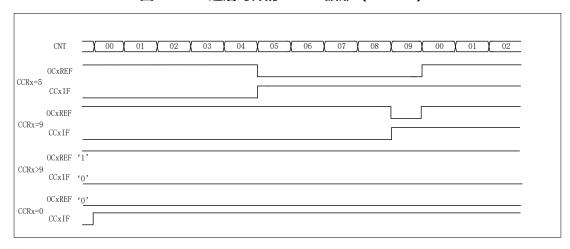

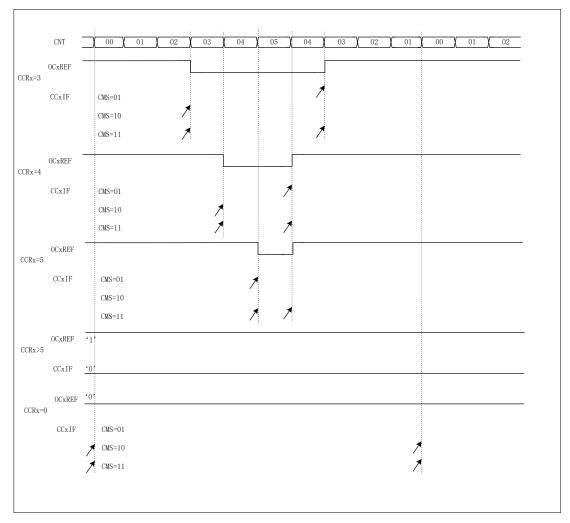

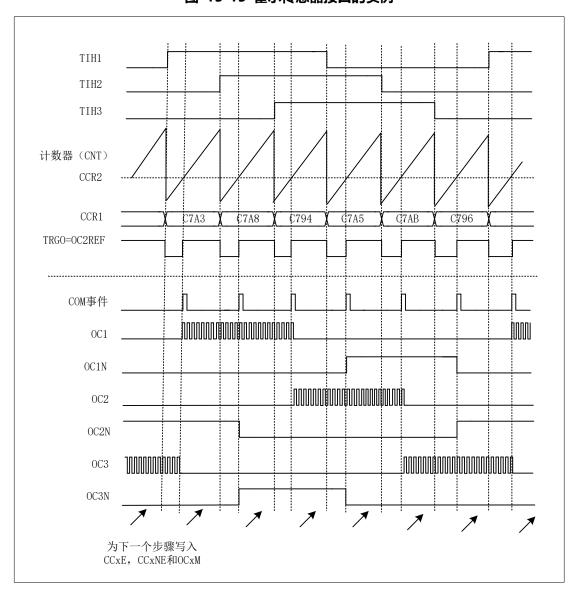

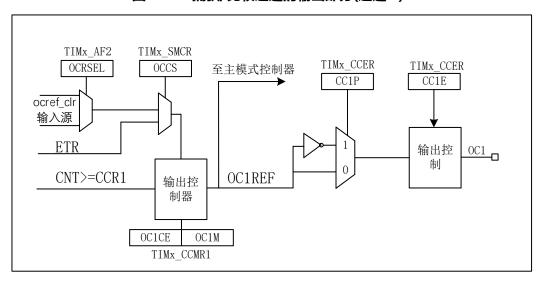

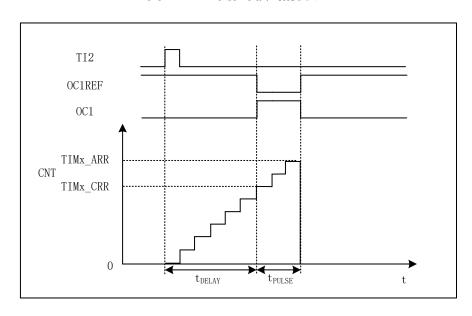

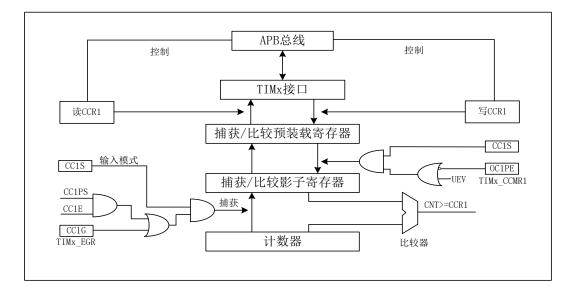

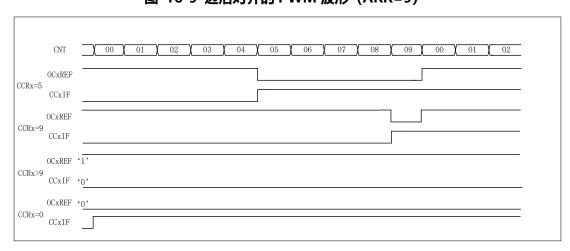

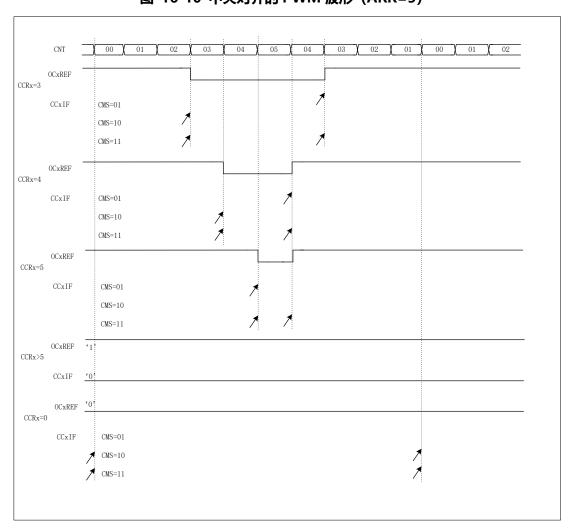

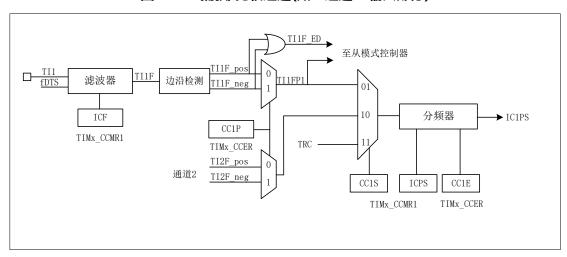

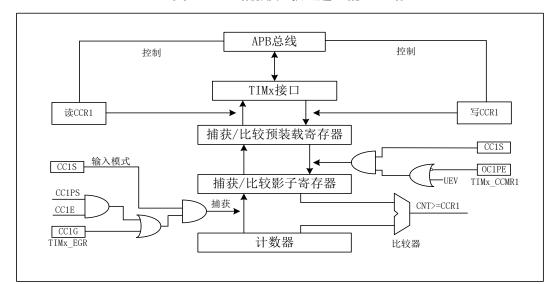

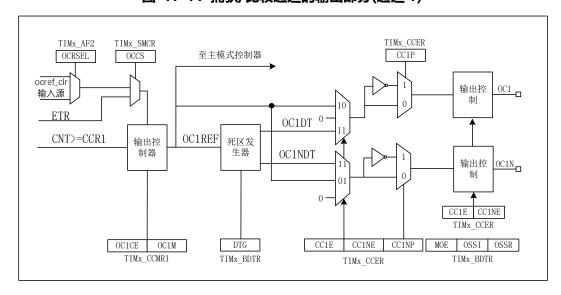

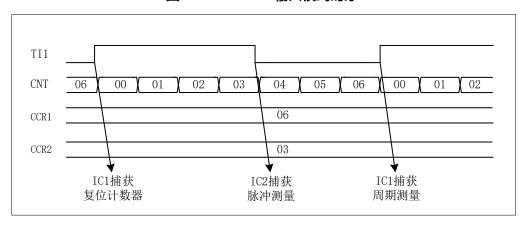

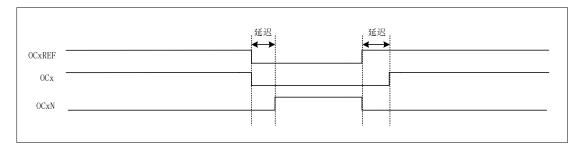

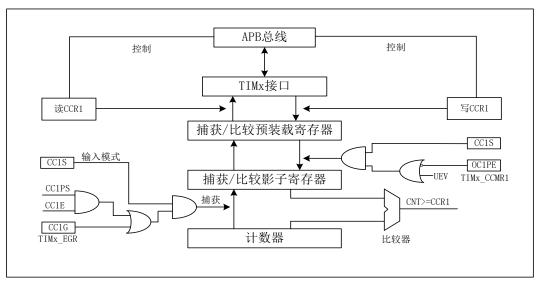

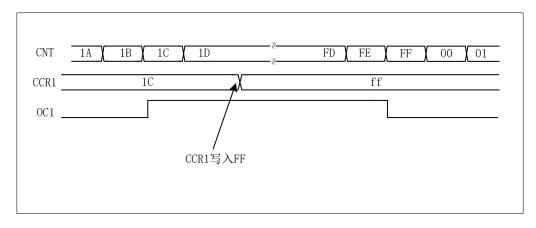

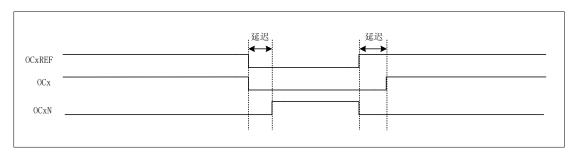

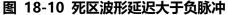

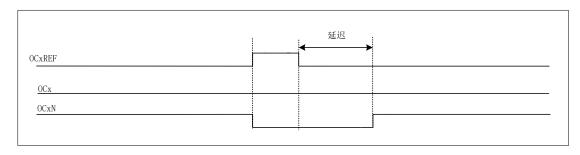

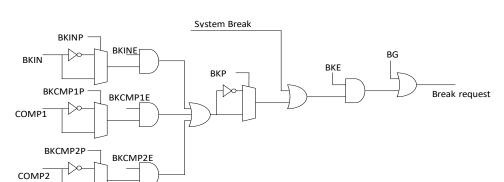

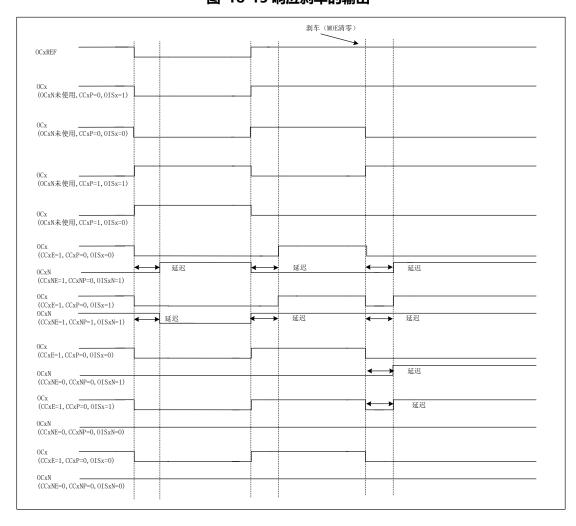

| 12.5.7. 捕获/比较通道                           | 221 |

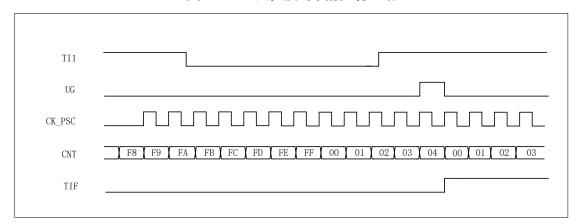

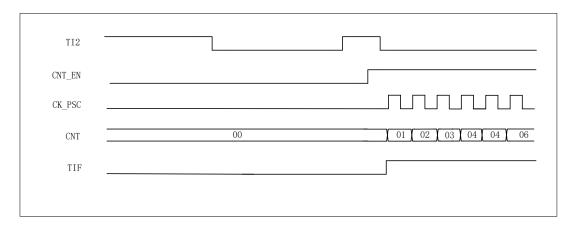

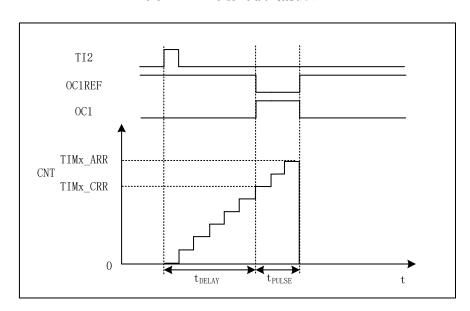

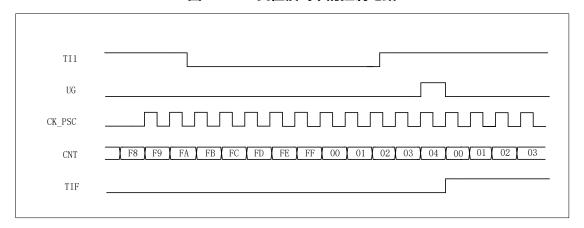

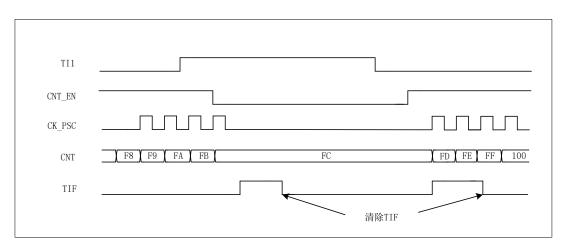

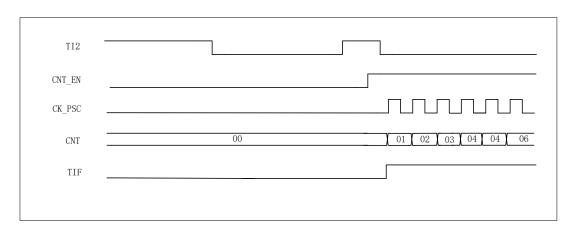

| 12.5.8. 定时器从模式                            | 235 |

| 12.5.9. 定时器 DMA 模式                        | 237 |

| 12.5.10. 定时器调试模式                          | 238 |

|     | 12.6. TIM1/8/20 寄存器描述                  | 238 |

|-----|----------------------------------------|-----|

|     | 12.6.1. 寄存器列表                          | 238 |

|     | 12.6.2. 控制寄存器 1(TIMx_CR1: 00h)         | 239 |

|     | 12.6.3. 控制寄存器 2(TIMx_CR2: 04h)         | 240 |

|     | 12.6.4. 从模式控制寄存器(TIMx_SMCR: 08h)       | 243 |

|     | 12.6.5. DMA/中断使能寄存器(TIMx_DIER: 0Ch)    | 245 |

|     | 12.6.6. 状态寄存器(TIMx_SR: 10h)            | 246 |

|     | 12.6.7. 事件产生寄存器(TIMx_EGR: 14h)         | 248 |

|     | 12.6.8. 捕获/比较模式寄存器 1(TIMx_CCMR1: 18h)  | 249 |

|     | 12.6.9. 捕获/比较模式寄存器 2(TIMx_CCMR2: 1Ch)  | 252 |

|     | 12.6.10. 捕获/比较使能寄存器(TIMx_CCER: 20h)    | 254 |

|     | 12.6.11. 计数器(TIMx_CNT: 24h)            | 257 |

|     | 12.6.12. 预分频器(TIMx_PSC: 28h)           | 257 |

|     | 12.6.13. 自动重装载寄存器(TIMx_ARR: 2Ch)       | 257 |

|     | 12.6.14. 重复计数寄存器(TIMx_RCR: 30h)        | 257 |

|     | 12.6.15. 捕获/比较寄存器 1(TIMx_CCR1: 34h)    | 258 |

|     | 12.6.16. 捕获/比较寄存器 2(TIMx_CCR2: 38h)    | 258 |

|     | 12.6.17. 捕获/比较寄存器 3(TIMx_CCR3: 3Ch)    | 258 |

|     | 12.6.18. 捕获/比较寄存器 4(TIMx_CCR4: 40h)    | 258 |

|     | 12.6.19. 刹车和死区寄存器(TIMx_BDTR: 44h)      | 259 |

|     | 12.6.20. DMA 控制寄存器(TIMx_DCR: 48h)      | 260 |

|     | 12.6.21. 连续模式的 DMA 地址(TIMx_DMAR: 4Ch)  | 261 |

|     | 12.6.22. 捕获/比较模式寄存器 3(TIMx_CCMR3: 54h) | 261 |

|     | 12.6.23. 捕获/比较寄存器 5(TIMx_CCR5: 58h)    | 263 |

|     | 12.6.24. 捕获/比较寄存器 6(TIMx_CCR6: 5Ch)    | 263 |

|     | 12.6.25. 复用功能选择寄存器 1(TIMx_AF1: 60h)    | 264 |

|     | 12.6.26. 复用功能选择寄存器 2(TIMx_AF2: 64h)    | 265 |

|     | 12.6.27. 输入选择寄存器(TIMx_TISEL: 68h)      | 265 |

|     | 12.6.28. DMA 请求类型选择寄存器(TIMx_DBER: 6Ch) | 266 |

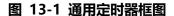

| 13. | 通用定时器(TIM2/3/4/5/23/24)                | 268 |

|     | 13.1. 概述                               | 268 |

|     | 13.2. 主要特性                             | 268 |

|     | 13.3. 结构框图                             | 269 |

|     | 13.4. TIMx 输入映射                        | 269 |

|     | 13.5. 功能描述                             | 271 |

|     | 13.5.1. 计数单元                           | 271 |

|     | 13.5.2. 预分频器                           | 272 |

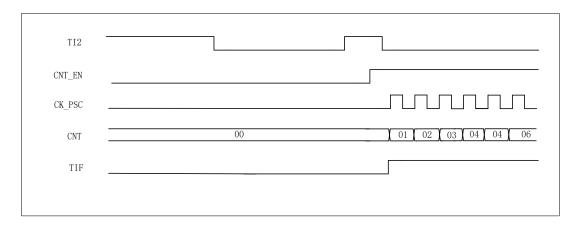

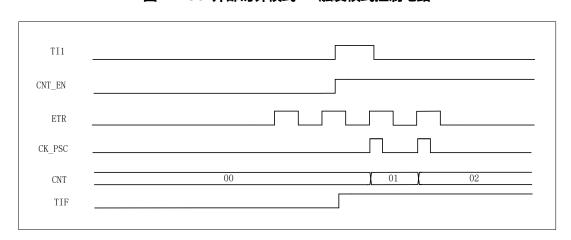

|     | 13.5.3. 时钟源选择                          | 272 |

|-----|----------------------------------------|-----|

|     | 13.5.4. 编码器模式                          | 273 |

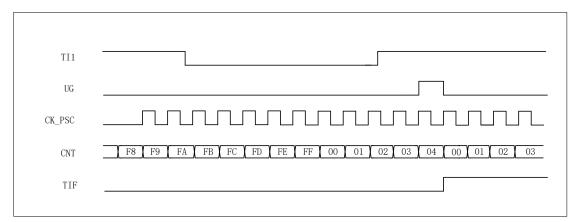

|     | 13.5.5. 捕获比较通道                         | 274 |

|     | 13.5.6. 定时器互连                          | 283 |

|     | 13.5.7. 定时器 DMA 模式                     | 285 |

|     | 13.5.8. 定时器调试模式                        | 285 |

|     | 13.6. TIM2/3/4/5/23/24 寄存器描述           | 286 |

|     | 13.6.1. 寄存器列表                          | 286 |

|     | 13.6.2. 控制寄存器 1(TIMx_CR1: 00h)         | 287 |

|     | 13.6.3. 控制寄存器 2(TIMx_CR2: 04h)         | 288 |

|     | 13.6.4. 从模式控制寄存器(TIMx_SMCR: 08h)       | 289 |

|     | 13.6.5. DMA/中断使能寄存器(TIMx_DIER: 0Ch)    | 291 |

|     | 13.6.6. 状态寄存器(TIMx_SR: 10h)            | 292 |

|     | 13.6.7. 事件产生寄存器(TIMx_EGR: 14h)         | 294 |

|     | 13.6.8. 捕获/比较模式寄存器 1(TIMx_CCMR1: 18h)  | 294 |

|     | 13.6.9. 捕获/比较模式寄存器 2(TIMx_CCMR2: 1Ch)  | 297 |

|     | 13.6.10. 捕获/比较使能寄存器(TIMx_CCER: 20h)    | 299 |

|     | 13.6.11. 计数器(TIMx_CNT: 24h)            | 300 |

|     | 13.6.12. 预分频器(TIMx_PSC: 28h)           | 300 |

|     | 13.6.13. 自动加载寄存器(TIMx_ARR: 2Ch)        | 301 |

|     | 13.6.14. 捕获/比较寄存器 1(TIMx_CCR1: 34h)    | 301 |

|     | 13.6.15. 捕获/比较寄存器 2(TIMx_CCR2: 38h)    | 301 |

|     | 13.6.16. 捕获/比较寄存器 3(TIMx_CCR3: 3Ch)    | 302 |

|     | 13.6.17. 捕获/比较寄存器 4(TIMx_CCR4: 40h)    | 302 |

|     | 13.6.18. DMA 控制寄存器(TIMx_DCR: 48h)      | 303 |

|     | 13.6.19. 连续模式的 DMA 地址(TIMx_DMAR: 4Ch)  | 304 |

|     | 13.6.20. 复用功能选择寄存器 1(TIMx_AF1: 60h)    | 304 |

|     | 13.6.21. 复用功能选择寄存器 2(TIMx_AF2: 64h)    | 304 |

|     | 13.6.22. 输入选择寄存器(TIMx_TISEL: 68h)      | 305 |

|     | 13.6.23. DMA 请求类型选择寄存器(TIMx_DBER: 6Ch) | 306 |

| 14. | . 基本定时器 (TIM6/7/21/22)                 | 308 |

|     | 14.1. 概述                               | 308 |

|     | 14.2. 主要特性                             | 308 |

|     | 14.3. 结构框图                             | 308 |

|     | 14.4. 功能描述                             | 308 |

|     | 14.4.1. 计数单元                           | 308 |

|     | 14.4.2. 预分频器                           | 309 |

| 14.4.3. 时钟源                         | 310     |

|-------------------------------------|---------|

| 14.4.4. 定时器调试模式                     | 310     |

| 14.5. TIM6/7/21/22 寄存器描述            | 310     |

| 14.5.1. 寄存器列表                       | 310     |

| 14.5.2. 控制寄存器 1(TIMx_CR1: 00h)      | 310     |

| 14.5.3. 控制寄存器 2(TIMx_CR2: 04h)      | 311     |

| 14.5.4. DMA/中断使能寄存器(TIMx_DIER: 0Ch) | 312     |

| 14.5.5. 状态寄存器(TIMx_SR: 10h)         | 312     |

| 14.5.6. 事件产生寄存器(TIMx_EGR: 14h)      | 313     |

| 14.5.7. 计数器(TIMx_CNT: 24h)          | 313     |

| 14.5.8. 预分频器(TIMx_PSC: 28h)         | 313     |

| 14.5.9. 自动重装载寄存器(TIMx_ARR: 2Ch)     | 314     |

| 15. 通用定时器 (TIM9/12)                 | 315     |

| 15.1. 概述                            | 315     |

| 15.2. 主要特性                          | 315     |

| 15.3. 结构框图                          | 316     |

| 15.4. TIMx 输入映射                     | 316     |

| 15.5. 功能描述                          | 317     |

| 15.5.1. 计数单元                        | 317     |

| 15.5.2. 预分频器                        | 318     |

| 15.5.3. 时钟源选择                       | 318     |

| 15.5.4. 捕获比较通道                      | 319     |

| 15.5.5. 定时器互连                       | 326     |

| 15.5.6. 定时器 DMA 模式                  | 327     |

| 15.5.7. 定时器调试模式                     | 328     |

| 15.6. TIM9/12 寄存器描述                 | 329     |

| 15.6.1. 寄存器列表                       | 329     |

| 15.6.2. 控制寄存器 1(TIMx_CR1: 00h)      | 329     |

| 15.6.3. 控制寄存器 2(TIMx_CR2: 04h)      | 331     |

| 15.6.4. 从模式控制寄存器(TIMx_SMCR: 08h)    |         |

| 15.6.5. DMA/中断使能寄存器(TIMx_DIER: 0Ch) |         |

| 15.6.6. 状态寄存器(TIMx_SR: 10h)         |         |

| 15.6.7. 事件产生寄存器(TIMx_EGR: 14h)      |         |

| 15.6.8. 捕获/比较模式寄存器 1(TIMx_CCMR1: 18 | 336)336 |

| 15.6.9. 捕获/比较使能寄存器(TIMx_CCER: 20h)  | 339     |

| 15.6.10. 计数器(TIMx_CNT: 24h)         | 340     |

| 15.6.11. 预分频器(TIMx_PSC: 28h)        | 340     |

| 15.6.12. 自动加载寄存器(TIMx_ARR: 2Ch)       | 340 |

|---------------------------------------|-----|

| 15.6.13. 捕获/比较寄存器 1(TIMx_CCR1: 34h)   | 340 |

| 15.6.14. 捕获/比较寄存器 2(TIMx_CCR2: 38h)   | 341 |

| 15.6.15. DMA 控制寄存器(TIMx_DCR: 48h)     | 341 |

| 15.6.16. 连续模式的 DMA 地址(TIMx_DMAR: 4Ch) | 342 |

| 15.6.17. 输入选择寄存器(TIMx_TISEL: 68h)     | 342 |

| 15.6.18. DMA 请求类型选择寄存器(TIMx_DBER: 6C  | h)  |

| 16. 通用定时器 (TIM10/11/13/14)            | 344 |

| 16.1. 概述                              | 344 |

| 16.2. 主 <del>要特</del> 性               | 344 |

| 16.3. 结构框图                            | 345 |

| 16.4. TIMx 输入映射                       | 345 |

| 16.5. 功能描述                            | 345 |

| 16.5.1. 计数单元                          | 345 |

| 16.5.2. 预分频器                          | 346 |

| 16.5.3. 时钟源选择                         |     |

| 16.5.4. 捕获比较通道                        | 348 |

| 16.5.5. 定时器互连                         |     |

| 16.5.6. 定时器 DMA 模式                    |     |

| 16.5.7. 定时器调试模式                       | 356 |

| 16.6. TIM10/11/13/14 寄存器描述            | 356 |

| 16.6.1. 寄存器列表                         | 356 |

| 16.6.2. 控制寄存器 1(TIMx_CR1: 00h)        |     |

| 16.6.3. 控制寄存器 2(TIMx_CR2: 04h)        |     |

| 16.6.4. 从模式控制寄存器(TIMx_SMCR: 08h)      |     |

| 16.6.5. DMA/中断使能寄存器(TIMx_DIER: 0Ch)   |     |

| 16.6.6. 状态寄存器(TIMx_SR: 10h)           |     |

| 16.6.7. 事件产生寄存器(TIMx_EGR: 14h)        |     |

| 16.6.8. 捕获/比较模式寄存器 1(TIMx_CCMR1: 18h) |     |

| 16.6.9. 捕获/比较使能寄存器(TIMx_CCER: 20h)    |     |

| 16.6.10. 计数器(TIMx_CNT: 24h)           |     |

| 16.6.11. 预分频器(TIMx_PSC: 28h)          |     |

| 16.6.12. 自动加载寄存器(TIMx_ARR: 2Ch)       |     |

| 16.6.13. 捕获/比较寄存器 1(TIMx_CCR1: 34h)   |     |

| 16.6.14. DMA 控制寄存器(TIMx_DCR: 48h)     | 367 |

| 16.6.15. 连续模式的 DMA 地址(TIMx_DMAR: 4Ch) | 368 |

| 16.6.16. 输入选择寄存器(TIMx_TISEL: 68h)     | 368 |

| 16.6.17. DMA 请求类型选择寄存器(TIMx_DBER: 6Ch) | 369 |

|----------------------------------------|-----|

| 17. 通用定时器(TIM15/25)                    | 370 |

| 17.1. 概述                               | 370 |

| 17.2. 主 <del>要特</del> 性                | 370 |

| 17.3. 结构框图                             | 371 |

| 17.4. TIMx 输入映射                        | 371 |

| 17.5. 功能描述                             | 372 |

| 17.5.1. 计数单元                           | 372 |

| 17.5.2. 预分频器                           | 373 |

| 17.5.3. 重复计数器                          | 374 |

| 17.5.4. 编码器模式                          | 374 |

| 17.5.5. 时钟源选择                          | 375 |

| 17.5.6. 捕获比较通道                         | 376 |

| 17.5.7. 定时器互连                          | 385 |

| 17.5.8. 定时器 DMA 模式                     | 387 |

| 17.5.9. 定时器调试模式                        | 388 |

| 17.6. TIM15/25 寄存器描述                   | 388 |

| 17.6.1. 寄存器列表                          | 388 |

| 17.6.2. 控制寄存器 1(TIMx_CR1: 00h)         | 389 |

| 17.6.3. 控制寄存器 2(TIMx_CR2: 04h)         | 390 |

| 17.6.4. 从模式控制寄存器(TIMx_SMCR: 08h)       | 391 |

| 17.6.5. DMA/中断使能寄存器(TIMx_DIER: 0Ch)    | 392 |

| 17.6.6. 状态寄存器(TIMx_SR: 10h)            | 393 |

| 17.6.7. 事件产生寄存器(TIMx_EGR: 14h)         | 394 |

| 17.6.8. 捕获/比较模式寄存器 1(TIMx_CCMR1: 18h)  | 395 |

| 17.6.9. 捕获/比较使能寄存器(TIMx_CCER: 20h)     | 398 |

| 17.6.10. 计数器(TIMx_CNT: 24h)            | 400 |

| 17.6.11. 预分频器(TIMx_PSC: 28h)           | 401 |

| 17.6.12. 自动重装载寄存器(TIMx_ARR: 2Ch)       | 401 |

| 17.6.13. 重复计数寄存器(TIMx_RCR: 30h)        | 401 |

| 17.6.14. 捕获/比较寄存器 1(TIMx_CCR1: 34h)    | 401 |

| 17.6.15. 捕获/比较寄存器 2(TIMx_CCR2: 38h)    | 402 |

| 17.6.16. 刹车和死区寄存器(TIMx_BDTR: 44h)      | 402 |

| 17.6.17. DMA 控制寄存器(TIMx_DCR: 48h)      | 404 |

| 17.6.18. 连续模式的 DMA 地址(TIMx_DMAR: 4Ch)  | 404 |

| 17.6.19. 复用功能选择寄存器(TIMx_AF1: 60h)      | 405 |

| 17.6.20. 复用功能选择寄存器 2(TIMx_AF2: 64h)    | 405 |

| 17.6.21. 输入选择寄存器(TIMx_TISEL: 68h)      | 406 |

|----------------------------------------|-----|

| 17.6.22. DMA 请求类型选择寄存器(TIMx_DBER: 6Ch) | 406 |

| 18. 通用定时器 (TIM16/17/18/19)             | 408 |

| 18.1. 概述                               | 408 |

| 18.2. 主要特性                             | 408 |

| 18.3. 结构框图                             | 409 |

| 18.4. TIMx 输入映射                        | 409 |

| 18.5. 功能描述                             | 409 |

| 18.5.1. 计数单元                           | 409 |

| 18.5.2. 预分频器                           | 410 |

| 18.5.3. 时钟源选择                          | 411 |

| 18.5.4. 重复计数器                          | 411 |

| 18.5.5. 捕获比较通道                         | 412 |

| 18.5.6. 定时器 DMA 模式                     | 419 |

| 18.5.7. 定时器调试模式                        | 420 |

| 18.6. TIM16/17/18/19 寄存器描述             | 420 |

| 18.6.1. 寄存器列表                          | 420 |

| 18.6.2. 控制寄存器 1(TIMx_CR1: 00h)         | 421 |

| 18.6.3. 控制寄存器 2(TIMx_CR2: 04h)         | 422 |

| 18.6.4. DMA/中断使能寄存器(TIMx_DIER: 0Ch)    | 423 |

| 18.6.5. 状态寄存器(TIMx_SR: 10h)            | 423 |

| 18.6.6. 事件产生寄存器(TIMx_EGR: 14h)         | 424 |

| 18.6.7. 捕获/比较模式寄存器 1(TIMx_CCMR1: 18h)  | 425 |

| 18.6.8. 捕获/比较使能寄存器(TIMx_CCER: 20h)     | 427 |

| 18.6.9. 计数器(TIMx_CNT: 24h)             | 429 |

| 18.6.10. 预分频器(TIMx_PSC: 28h)           | 430 |

| 18.6.11. 自动重装载寄存器(TIMx_ARR: 2Ch)       | 430 |

| 18.6.12. 重复计数寄存器(TIMx_RCR: 30h)        | 430 |

| 18.6.13. 捕获/比较寄存器 1(TIMx_CCR1: 34h)    | 430 |

| 18.6.14. 刹车和死区寄存器(TIMx_BDTR: 44h)      | 431 |

| 18.6.15. DMA 控制寄存器(TIMx_DCR: 48h)      | 432 |

| 18.6.16. 连续模式的 DMA 地址(TIMx_DMAR: 4Ch)  | 433 |

| 18.6.17. 复用功能选择寄存器(TIMx_AF1: 60h)      | 433 |

| 18.6.18. 复用功能选择寄存器 2(TIMx_AF2: 64h)    | 434 |

| 18.6.19. 输入选择寄存器(TIMx_TISEL: 68h)      | 435 |

| 18.6.20. DMA 请求类型选择寄存器(TIMx_DBER: 6Ch) | 435 |

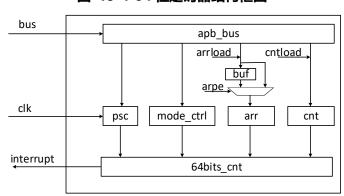

| 19. 64 位定时器(TIM26)                     | 437 |

| 19.1. 概述                                 | 437 |

|------------------------------------------|-----|

| 19.2. 主要特性                               | 437 |

| 19.2.1. 结构框图                             | 437 |

| 19.2.2. 功能描述                             | 437 |

| 19.3. TIM 寄存器描述                          | 437 |

| 19.3.1. 控制寄存器(TIM64B_CTRL: 00h)          | 438 |

| 19.3.2. 状态寄存器(TIM64B_SR: 04h)            | 438 |

| 19.3.3. 自动重装载寄存器低 32 位(TIM64B_ARRL: 08h) | 439 |

| 19.3.4. 自动重装载寄存器高 32 位(TIM64B_ARRH: 0Ch) | 439 |

| 19.3.5. 计数器低 32 位(TIM64B_CNTL: 10h)      | 439 |

| 19.3.6. 计数器高 32 位(TIM64B_CNTH: 14h)      | 439 |

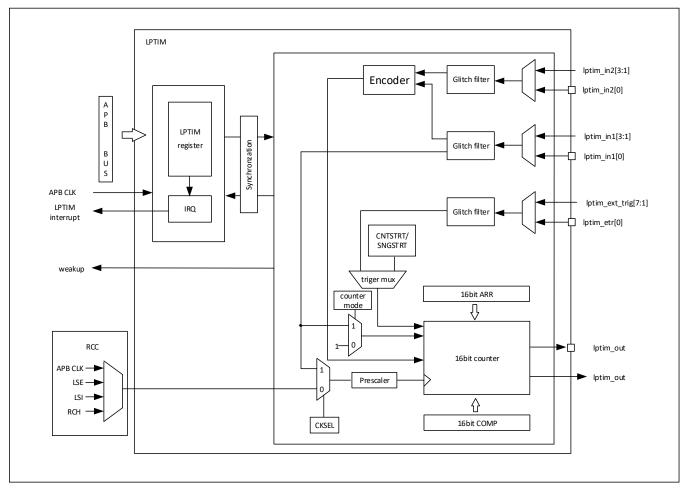

| 20. 低功耗定时器 (LPTIM)                       | 440 |

| 20.1. 概述                                 | 440 |

| 20.2. 主要特性                               | 440 |

| 20.3. 结构框图                               | 441 |

| 20.4. 功能说明                               | 441 |

| 20.4.1. 触发映射                             | 441 |

| 20.4.2. 复位和时钟                            | 442 |

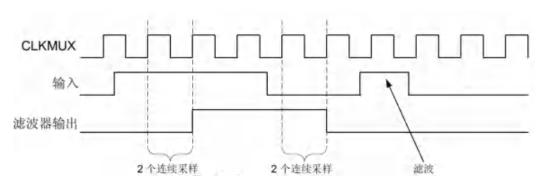

| 20.4.3. 干扰滤波器                            | 442 |

| 20.4.4. 预分频器                             | 442 |

| 20.4.5. 触发多路复用器                          | 443 |

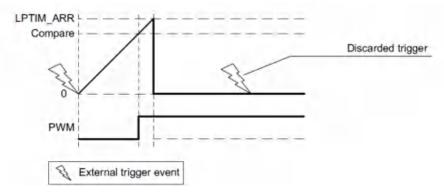

| 20.4.6. 工作模式                             | 443 |

| 20.4.7. 超时功能                             | 445 |

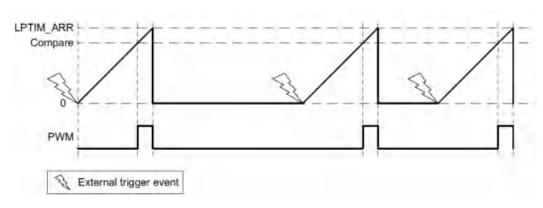

| 20.4.8. 生成波形                             | 446 |

| 20.4.9. 寄存器更新                            | 447 |

| 20.4.10. 计数器模式                           | 447 |

| 20.4.11. 定时器使能                           | 448 |

| 20.4.12. 定时器计数器复位                        | 448 |

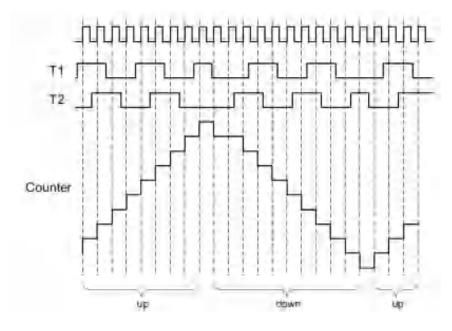

| 20.4.13. 编码器模式                           | 448 |

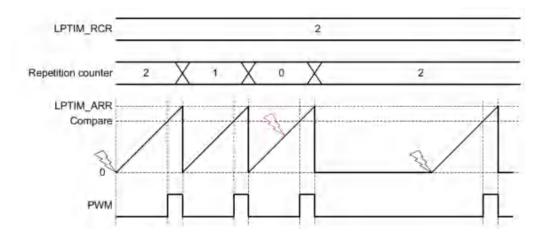

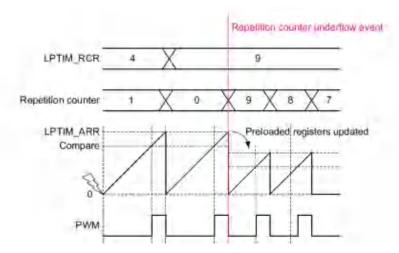

| 20.4.14. 重复计数器                           | 449 |

| 20.5. LPTIM 低功耗模式                        | 450 |

| 20.6. LPTIM 中断                           | 450 |

| 20.7. LPTIM 寄存器描述                        | 451 |

| 20.7.1. 寄存器列表                            | 451 |

| 20.7.2. 中断和状态寄存器(LPTIM_ISR: 00h)         | 452 |

| 20.7.3. 中断清零寄存器(LPTIM_ICR: 04h)          | 453 |

| 20.7.4. 中断使能寄存器(LPTIM_IER: 08h)          | 454 |

|     | 20.7.5. 配置寄存器 1 LPTIM_CFGR1: 0Ch)      | 455 |

|-----|----------------------------------------|-----|

|     | 20.7.6. 控制寄存器(LPTIM_CR: 10h)           | 458 |

|     | 20.7.7. 比较寄存器(LPTIM_CMP: 14h)          | 459 |

|     | 20.7.8. 自动重载寄存器(LPTIM_ARR: 18h)        | 459 |

|     | 20.7.9. 计数器寄存器(LPTIM_CNT: 1Ch)         | 460 |

|     | 20.7.10. 配置寄存器 2 LPTIM_CFGR2: 24h)     | 460 |

|     | 20.7.11. 重复寄存器(LPTIM_RCR: 28h)         | 461 |

| 21. | 系统看门狗 (WDT)                            | 462 |

|     | 21.1. 概述                               | 462 |

|     | 21.2. 主要特性                             | 462 |

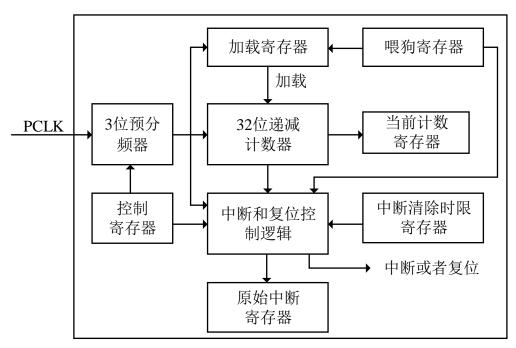

|     | 21.3. 功能描述                             | 462 |

|     | 21.3.1. 结构框图                           | 463 |

|     | 21.3.2. 时钟分频                           | 463 |

|     | 21.3.3. 启动看门狗                          | 463 |

|     | 21.3.4. 递减计数器                          | 463 |

|     | 21.3.5. 中断模式                           | 463 |

|     | 21.3.6. 复位模式                           | 464 |

|     | 21.4. 配置流程                             | 464 |

|     | 21.4.1. 中断模式                           | 464 |

|     | 21.4.2. 复位模式                           | 464 |

|     | 21.5. WDT 寄存器描述                        | 465 |

|     | 21.5.1. 寄存器列表                          | 465 |

|     | 21.5.2. 加载寄存器(WDT_LOAD: 00h)           | 465 |

|     | 21.5.3. 当前计数寄存器(WDT_COUNT: 04h)        | 465 |

|     | 21.5.4. 控制寄存器(WDT_CTRL: 08h)           | 465 |

|     | 21.5.5. 喂狗寄存器(WDT_FEED: 0Ch)           | 466 |

|     | 21.5.6. 中断清除时限寄存器(WDT_INTCLRTIME: 10h) | 466 |

|     | 21.5.7. 原始中断状态寄存器(WDT_RIS: 14h)        | 466 |

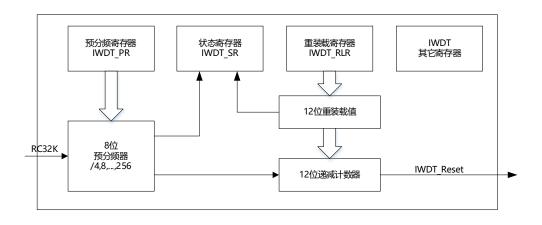

| 22. | 独立看门狗(IWDT)                            | 467 |

|     | 22.1. 概述                               | 467 |

|     | 22.2. 主要特性                             | 467 |

|     | 22.3. 功能描述                             | 467 |

|     | 22.3.1. 结构框图                           | 467 |

|     | 22.3.2. 时钟                             | 468 |

|     | 22.3.3. 预分频                            |     |

|     | 22.3.4. 寄存器访问保护                        | 468 |

|     | 22.3.5. 窗口选项                           | 468 |

| 22.3.6. 唤醒功能                  | 469 |

|-------------------------------|-----|

| 22.3.7. 低功耗                   | 469 |

| 22.3.8. IWDT 复位               | 470 |

| 22.4. 配置流程                    | 470 |

| 22.5. IWDT 寄存器描述              | 471 |

| 22.5.1. 寄存器列表                 | 471 |

| 22.5.2. 命令寄存器(IWDT_CMDR: 00h) | 471 |

| 22.5.3. 预分频寄存器(IWDT_PR: 04h)  | 471 |

| 22.5.4. 重装载寄存器(IWDT_RLR: 08h) | 472 |

| 22.5.5. 状态寄存器(IWDT_SR: 0Ch)   | 472 |

| 22.5.6. 窗口寄存器(IWDT_WINR: 10h) | 473 |

| 22.5.7. 唤醒寄存器(IWDT_WUTR: 14h) | 473 |

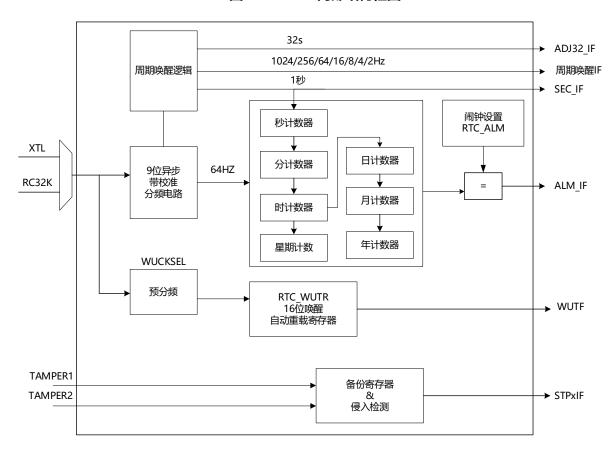

| 23. 实时时钟 (RTC)                | 474 |

| 23.1. 概述                      | 474 |

| 23.2. 主要特性                    | 474 |

| 23.3. 功能描述                    | 474 |

| 23.3.1. 结构框图                  | 474 |

| 23.3.2. 复位过程                  | 475 |

| 23.3.3. 时间和日历                 | 475 |

| 23.3.4. 闹钟功能                  | 476 |

| 23.3.5. 时钟误差补偿                | 476 |

| 23.3.6. RTC 输出                | 477 |

| 23.3.7. 周期中断唤醒                | 477 |

| 23.3.8. 侵入检测和时间戳              | 478 |

| 23.3.9. 备份寄存器                 | 478 |

| 23.3.10. RTC 低功耗              | 478 |

| 23.3.11. RTC 中断               | 479 |

| 23.4. 配置流程                    | 480 |

| 23.4.1. RTC 模块使能流程            | 480 |

| 23.4.2. RTC 时间设置流程            | 480 |

| 23.4.3. RTC 时间读取流程            | 480 |

| 23.4.4. RTC 闹钟设置流程            | 480 |

| 23.4.5. 唤醒定时器设置流程             | 481 |

| 23.4.6. 侵入检测设置流程              | 481 |

| 23.4.7. RTC 中断和唤醒设置流程         | 481 |

| 23.5. RTC 寄存器描述               | 482 |

| 23.5.1. 寄存器列表                 | 482 |

|     | 23.5.2. 写保护寄存器(RTC_WP: 00h)                 | 482 |

|-----|---------------------------------------------|-----|

|     | 23.5.3. 中断使能寄存器(RTC_IE: 04h)                | 482 |

|     | 23.5.4. 中断标志寄存器(RTC_SR: 08h)                | 484 |

|     | 23.5.5. 秒计数寄存器(RTC_SEC: 0Ch)                | 486 |

|     | 23.5.6. 分钟计数寄存器(RTC_MIN: 10h)               | 486 |

|     | 23.5.7. 小时计数寄存器(RTC_HOUR: 14h)              | 486 |

|     | 23.5.8. 日计数寄存器(RTC_DAY: 18h)                | 486 |

|     | 23.5.9. 周计数寄存器(RTC_WEEK: 1Ch)               | 486 |

|     | 23.5.10. 月计数寄存器(RTC_MONTH: 20h)             | 487 |

|     | 23.5.11. 年计数寄存器(RTC_YEAR: 24h)              | 487 |

|     | 23.5.12. 闹钟寄存器(RTC_ALARM: 28h)              | 487 |

|     | 23.5.13. 控制寄存器(RTC_CR: 2Ch)                 | 487 |

|     | 23.5.14. 时钟误差补偿寄存器(RTC_ ADJUST: 30h)        | 490 |

|     | 23.5.15. 时间戳寄存器 1 (RTC_CLKSTAMP1: 44h)      | 490 |

|     | 23.5.16. 日历戳寄存器 1 (RTC_CALSTAMP1: 48h)      | 491 |

|     | 23.5.17. 时间戳寄存器 2 (RTC_CLKSTAMP2: 4Ch)      | 491 |

|     | 23.5.18. 日历戳寄存器 2 (RTC_CALSTAMP2: 50h)      | 491 |

|     | 23.5.19. 唤醒定时器寄存器(RTC_WUTR: 54h)            | 491 |

|     | 23.5.20. 备份寄存器 0~15 (RTC_BAKUP0~15: 70~ACh) | 492 |

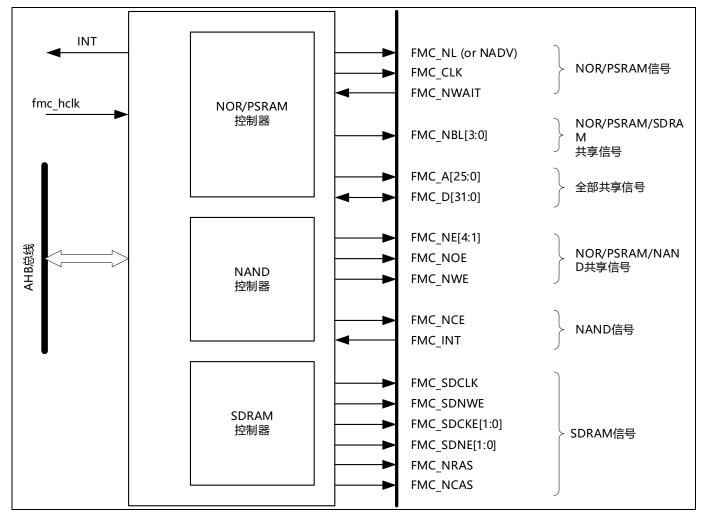

| 24. | . 外部存储器控制器(FMC)                             | 493 |

|     | 24.1. 概述                                    | 493 |

|     | 24.2. 主要特性                                  | 493 |

|     | 24.3. 功能描述                                  | 494 |

|     | 24.3.1. 结构框图                                | 494 |

|     | 24.3.2. AHB 接口                              | 494 |

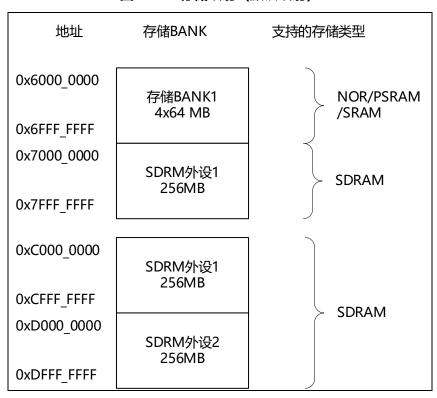

|     | 24.3.3. 外部器件地址映射                            | 495 |

| 25. | . NOR Flash/PSRAM 控制器(FMC_NORSRAM)          | 498 |

|     | 25.1. 概述                                    | 498 |

|     | 25.2. 主要特性                                  | 498 |

|     | 25.3. 功能说明                                  | 498 |

|     | 25.3.1. 外部存储器接口信号                           | 499 |

|     | 25.3.2. 支持的存储器和事务                           | 500 |

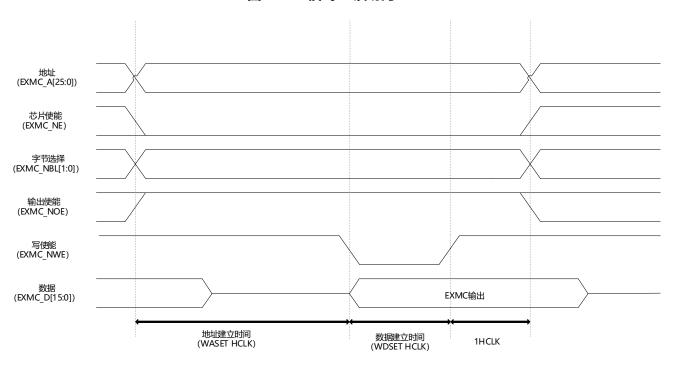

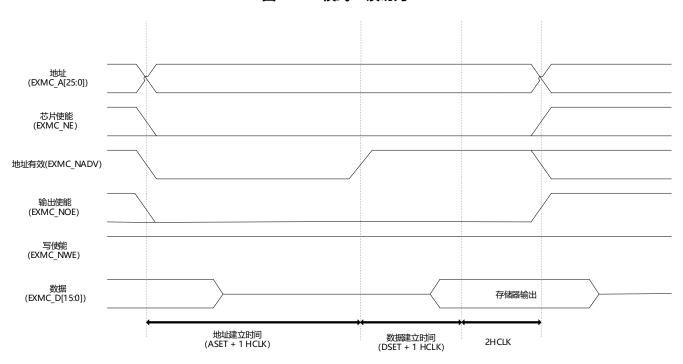

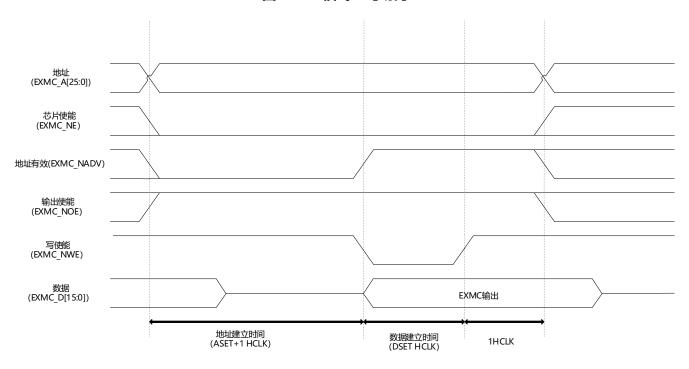

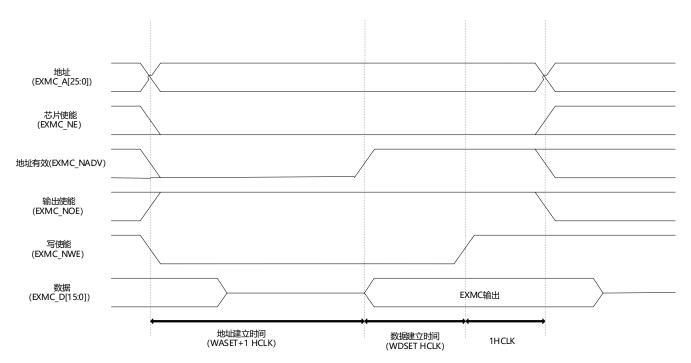

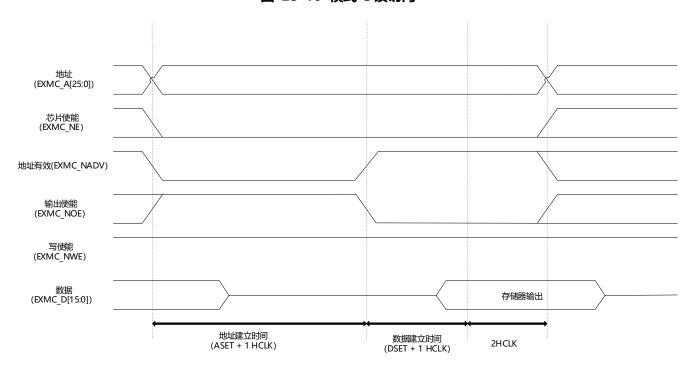

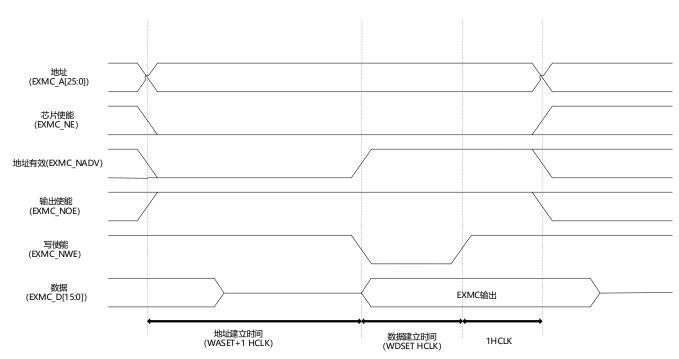

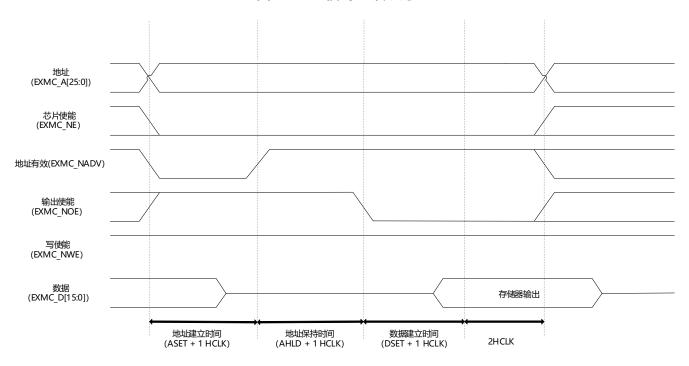

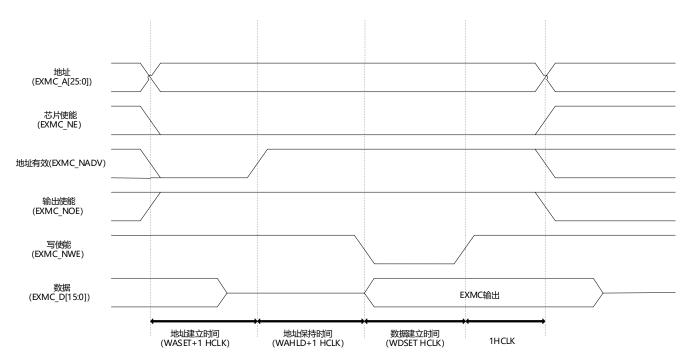

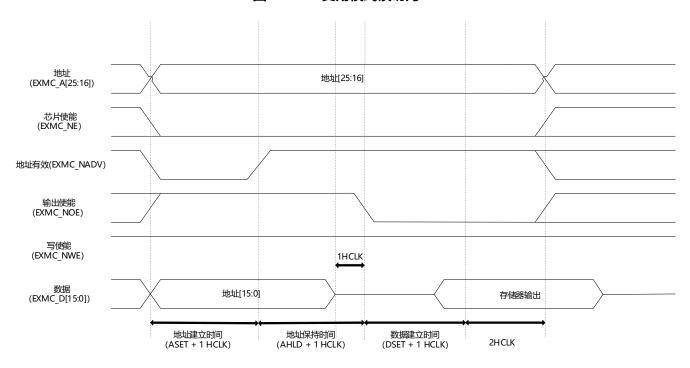

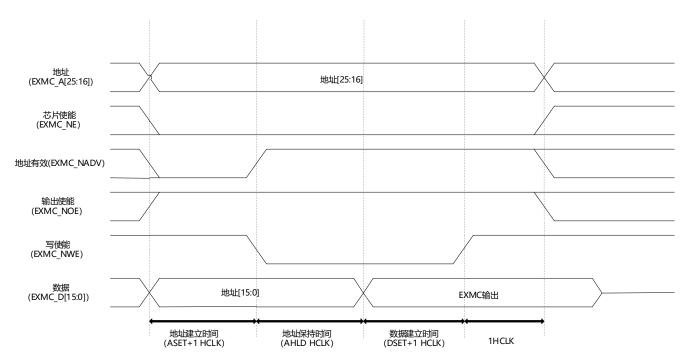

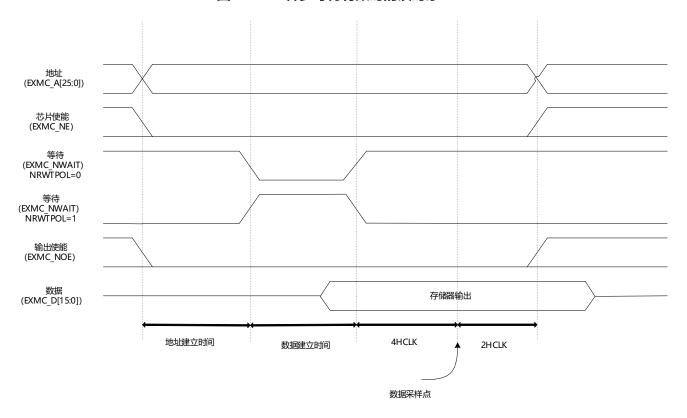

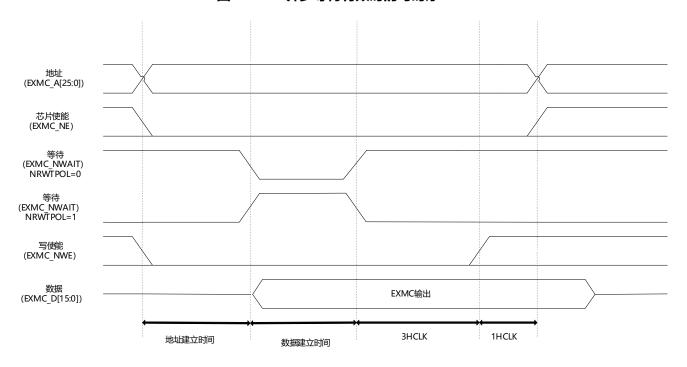

|     | 25.3.3. 通用时序                                | 501 |

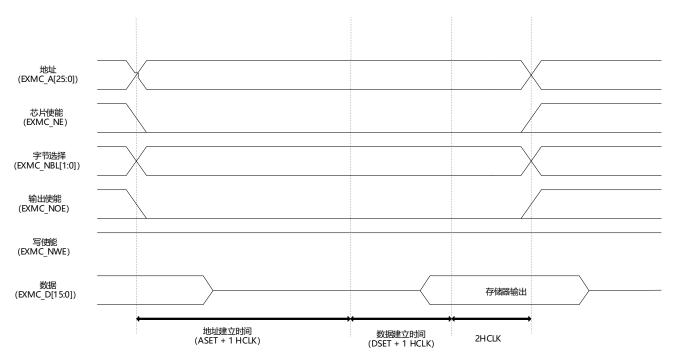

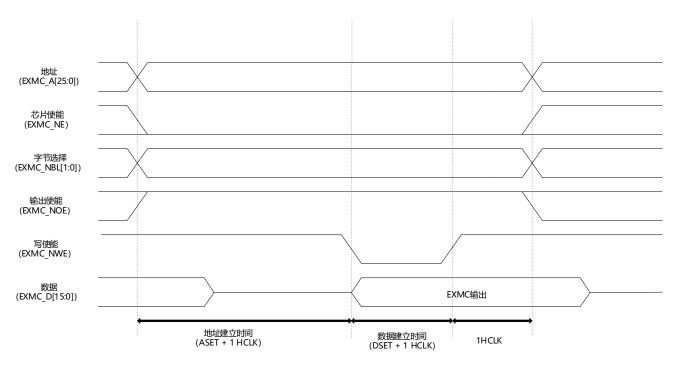

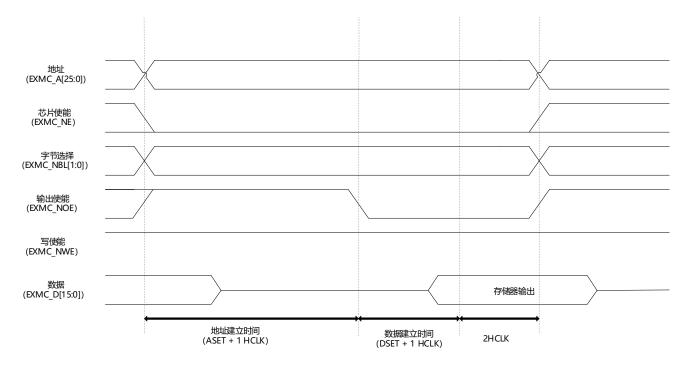

|     | 25.3.4. 异步事务                                | 501 |

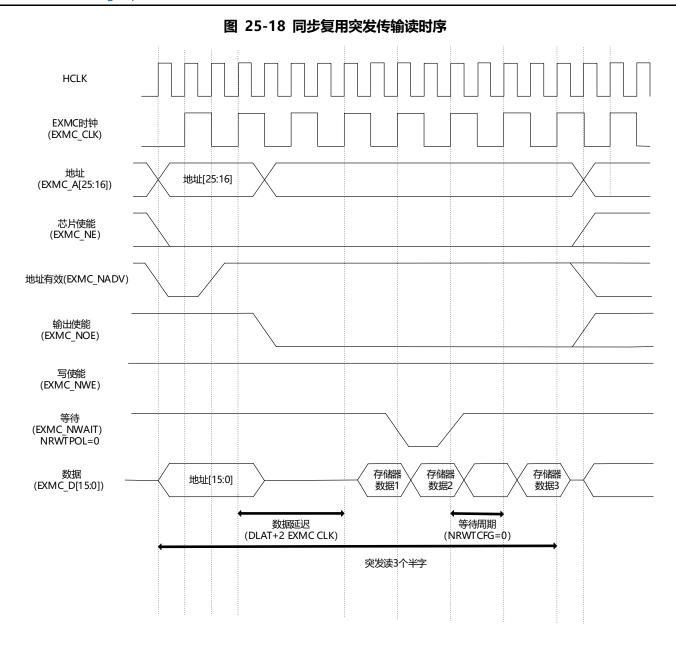

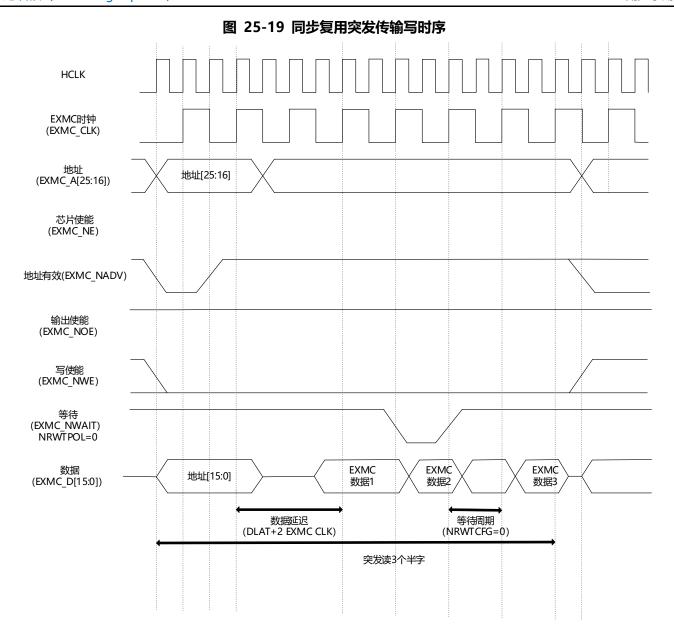

|     | 25.3.5. 同步事务                                | 515 |

|     | 25.4. 配置流程                                  | 520 |

|     | 25.4.1. Nor 闪存设置流程                          | 520 |

| 25.4.2. PSRAM 设置流程                                            | 520 |

|---------------------------------------------------------------|-----|

| 25.4.3. SRAM 设置流程                                             | 520 |

| 25.4.4. LCD8080 设置流程                                          | 521 |

| 25.5. FMC_NORSRAM 寄存器描述                                       | 521 |

| 25.5.1. 寄存器列表                                                 | 521 |

| 25.5.2. NORSRAM 控制寄存器 1~4(FMC_SNCTLx: 00h+8*(x-1), x=1~4)     | 521 |

| 25.5.3. NORSRAM 时序配置寄存器 1~4(FMC_SNTCFGx: 04h+8*(x-1), x=1~4)  | 523 |

| 25.5.4. NORSRAM 写时序寄存器 1~4(FMC_SNWTCFGx: 104h+8*(x-1), x=1~4) | 524 |

| 26. SDRAM 控制器 (FMC_SDRAM)                                     | 526 |

| 26.1. 概述                                                      | 526 |

| 26.2. 主要特性                                                    | 526 |

| 26.3. SDRAM 外部存储器接口信号                                         | 526 |

| 26.4. 功能描述                                                    | 527 |

| 26.4.1. SDRAM 初始化                                             | 527 |

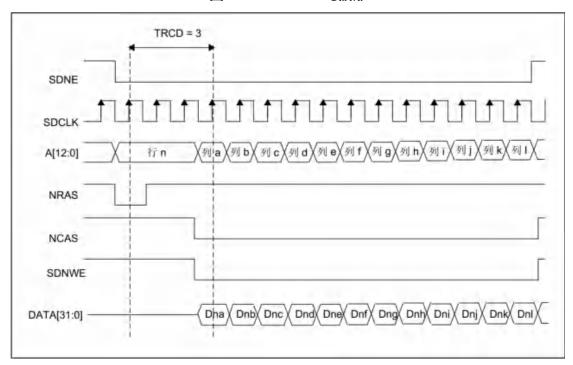

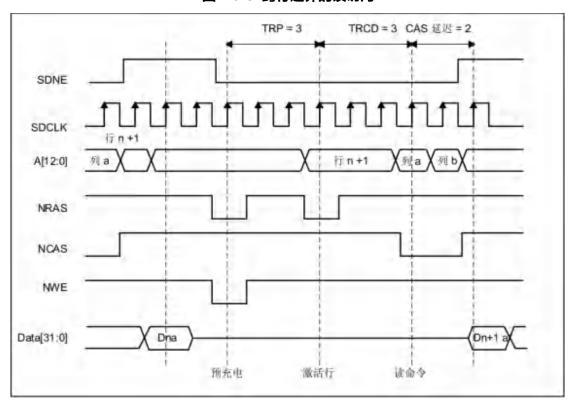

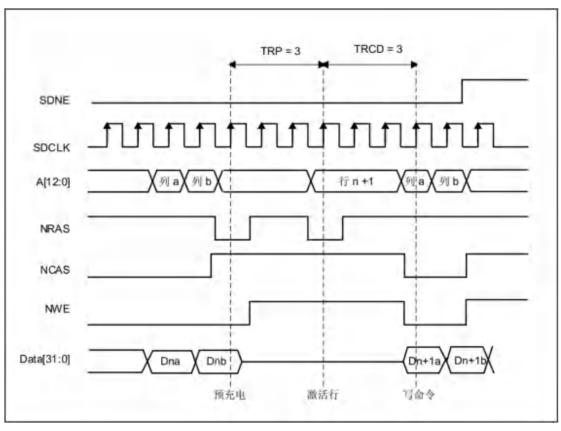

| 26.4.2. SDRAM 写访问                                             | 527 |

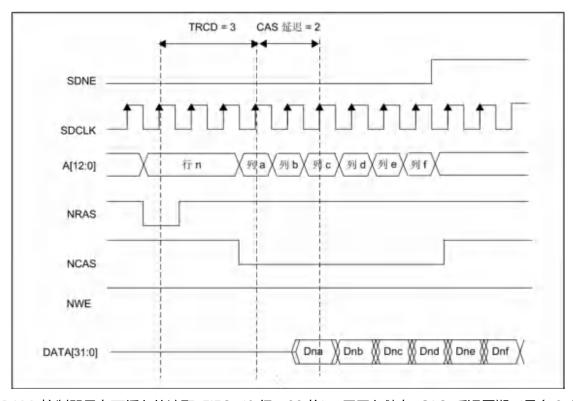

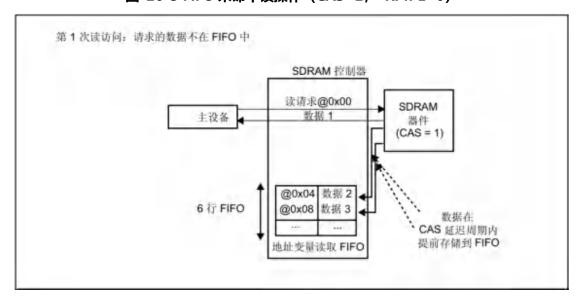

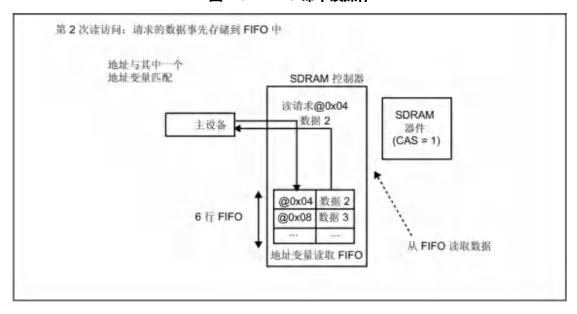

| 26.4.3. SDRAM 读访问                                             | 528 |

| 26.4.4. 行和 Bank 边界管理                                          | 530 |

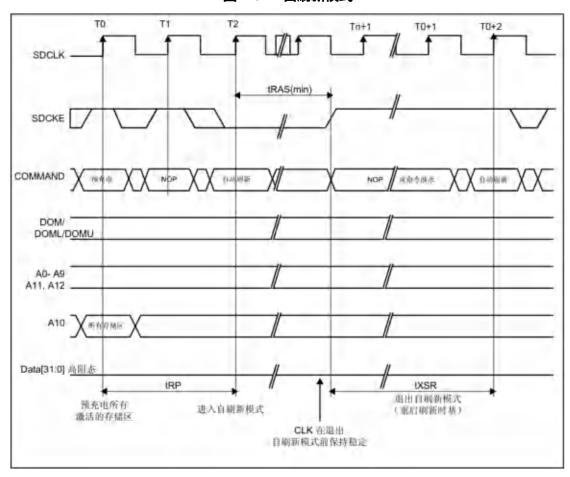

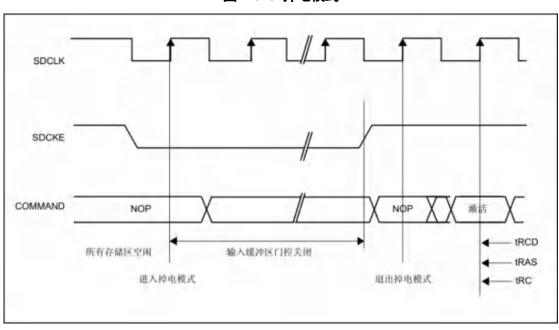

| 26.4.5. SDRAM 刷新周期                                            | 532 |

| 26.4.6. 低功耗模式                                                 | 532 |

| 26.5. FMC_SDRAM 控制器寄存器描述                                      | 534 |

| 26.5.1. 寄存器列表                                                 | 534 |

| 26.5.2. 控制寄存器 1,2(FMC_SDRCRx: 00h+4*(x−1), x=1,2)             | 534 |

| 26.5.3. 时序寄存器 1,2(FMC_SDRTRx: 08h+4*(x−1), x = 1,2)           | 536 |

| 26.5.4. 命令模式寄存器 (FMC_SDRCMD: 10h)                             | 538 |

| 26.5.5. 刷新定时器寄存器 (FMC_SDRART: 14h)                            | 539 |

| 26.5.6. 状态寄存器 (FMC_SDRSR: 18h)                                | 540 |

| 26.5.7. 采样微调寄存器 1(FMC_SDRSMA1: 1Ch)                           | 541 |

| 26.5.8. 采样微调寄存器 2(FMC_SDRSMA2: 20h)                           | 541 |

| 27. NAND Flash 控制器(FMC_NAND)                                  | 542 |

| 27.1. 概述                                                      | 542 |

| 27.2. 主要特性                                                    | 542 |

| 27.3. 功能描述                                                    | 542 |

| 27.3.1. 外部存储接口信号                                              | 542 |

| 27.3.2. NAND Flash 支持的存储器和事务                                  | 542 |

| 27.3.3. 数据通道访问配置                                              | 543 |

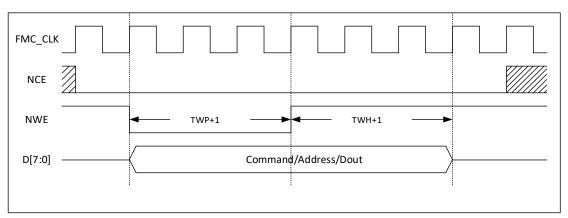

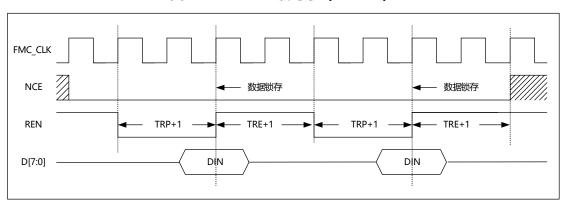

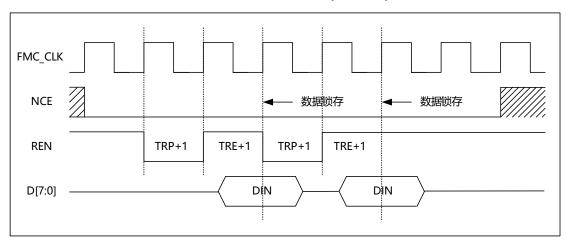

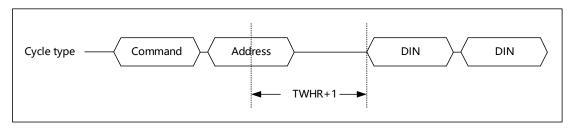

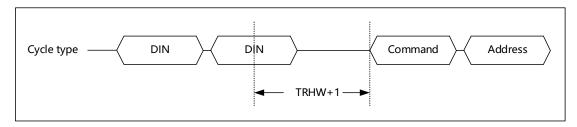

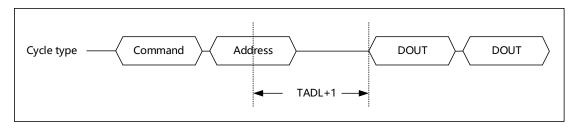

| 27.3.4. NAND Flash 的时序图                                       | 543 |

| 27.3.5. NAND Flash 操作                                         | 545 |

|     | 27.3.6. BCH 操作                                   | 545 |

|-----|--------------------------------------------------|-----|

|     | 27.4. FMC_NAND 寄存器描述                             | 546 |

|     | 27.4.1. 寄存器列表                                    | 546 |

|     | 27.4.2. NFM 控制寄存器(FMC_NFMCTRL: 00h)              | 547 |

|     | 27.4.3. NFM 等待寄存器(FMC_NFMWST: 04h)               | 547 |

|     | 27.4.4. NFM 状态寄存器(FMC_NFMSTATUS: 08h)            | 548 |

|     | 27.4.5. BCH 配置寄存器(FMC_BCH_CONFIG: 10h)           | 548 |

|     | 27.4.6. BCH 控制寄存器(FMC_BCH_CTRL: 14h)             | 548 |

|     | 27.4.7. BCH 状态寄存器(FMC_BCH_STATUS: 18h)           | 549 |

|     | 27.4.8. BCH 校验码寄存器(FMC_BCH_CODE: 1Ch)            | 550 |

|     | 27.4.9. BCH 错误地址寄存器(FMC_BCH_ERRADR: 20h)         | 550 |

|     | 27.4.10. BCH 错误向量寄存器(FMC_BCH_ERRVEC: 24h)        | 550 |

|     | 27.4.11. BCH 纠错基地址寄存器(FMC_BCH_BASEADDR: 28h)     | 550 |

|     | 27.4.12. BCH 校验码指针寄存器(FMC_BCH_CODEPTR: 2Ch)      | 550 |

|     | 27.4.13. BCH 错误地址指针寄存器(FMC_BCH_ERRADDRPTR: 30h)  | 551 |

|     | 27.4.14. BCH 错误向量指针寄存器(FMC_BCH_ERRVECPTR: 34h)   | 551 |

|     | 27.4.15. BCH 页记数寄存器(FMC_BCH_PAGENUM: 38h)        | 551 |

|     | 27.4.16. BCH 地址锁存寄存器(FMC_BCH_ADDRLATCH: 3Ch)     | 551 |

|     | 27.4.17. NFM 命令通道寄存器(FMC_NFMCMD: 40h)            | 551 |

|     | 27.4.18. NFM 地址通道寄存器(FMC_NFMADDR: 44h)           | 551 |

|     | 27.4.19. NFM ECC 数据通道寄存器(FMC_NFMECCDATA: 48h)    | 552 |

|     | 27.4.20. NFM 非 ECC 数据通道寄存器(FMC_NFMNECCDATA: 4Ch) | 552 |

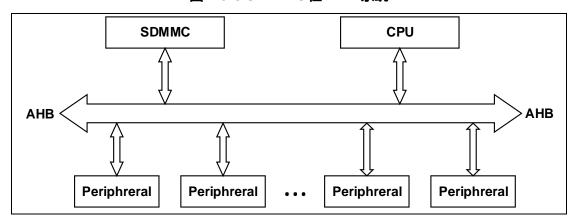

| 28. | 安全数字输入/输出多媒体卡接口(SDMMC)                           | 553 |

|     | 28.1. 概述                                         | 553 |

|     | 28.2. 主要特性                                       | 553 |

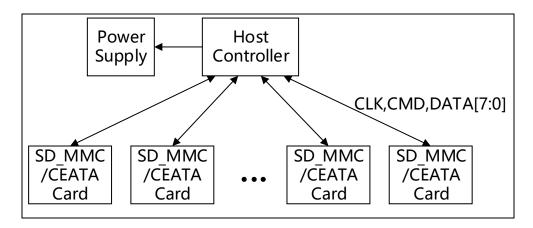

|     | 28.3. 总线拓扑                                       | 554 |

|     | 28.3.1. 拓扑框图                                     | 554 |

|     | 28.3.2. 总线描述                                     | 554 |

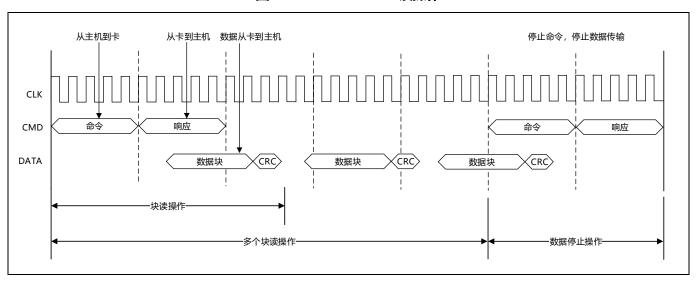

|     | 28.4. 功能描述                                       | 556 |

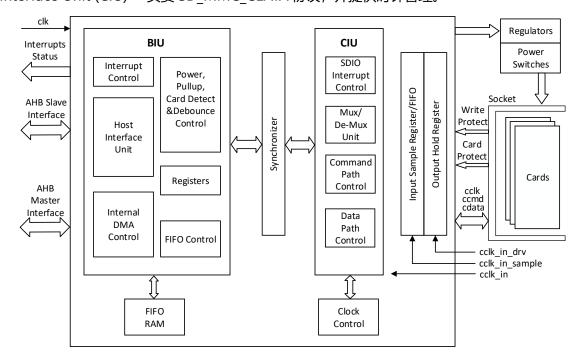

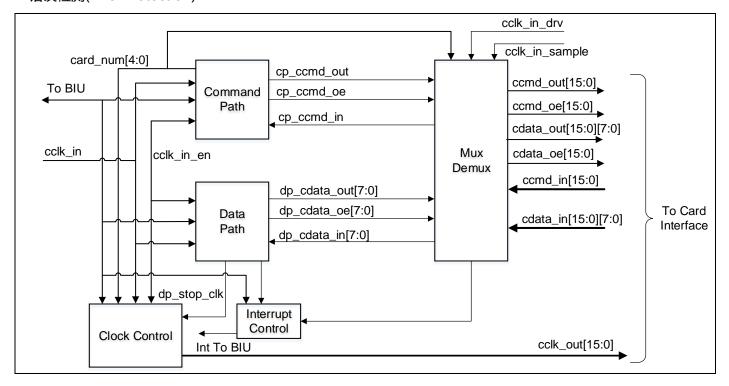

|     | 28.4.1. 结构框图                                     | 556 |

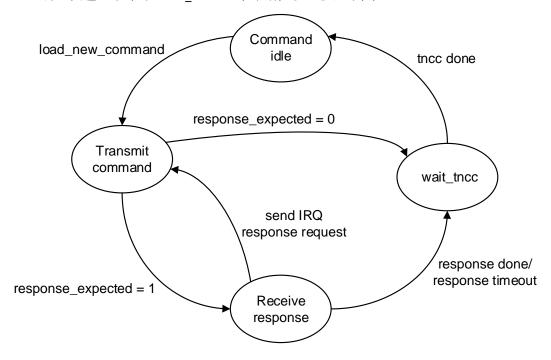

|     | 28.4.2. 总线接口单元                                   | 557 |

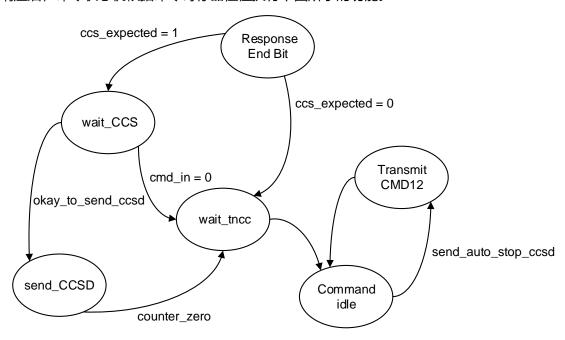

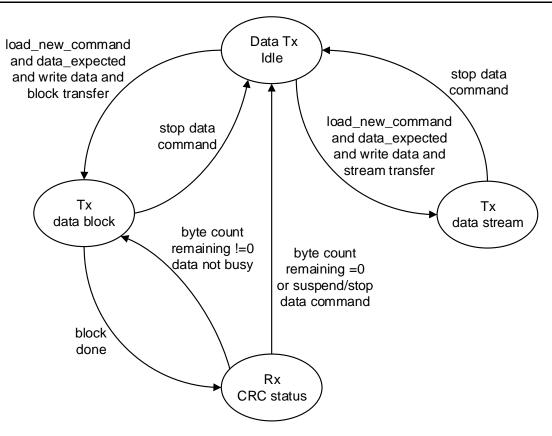

|     | 28.4.3. 卡接口单元                                    | 560 |

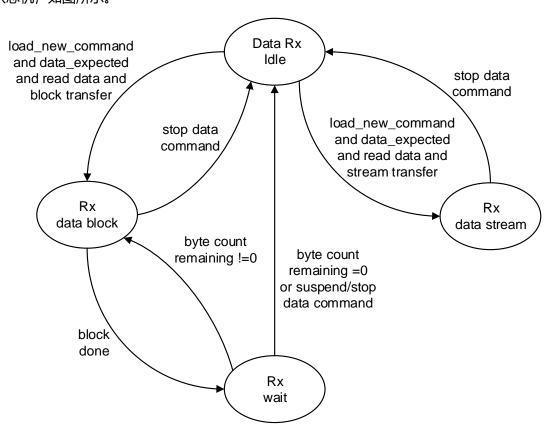

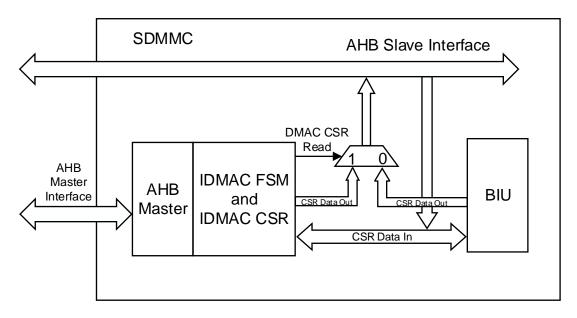

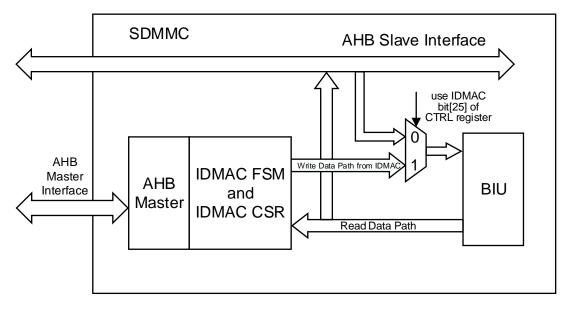

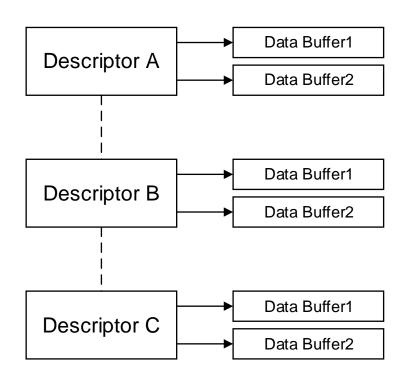

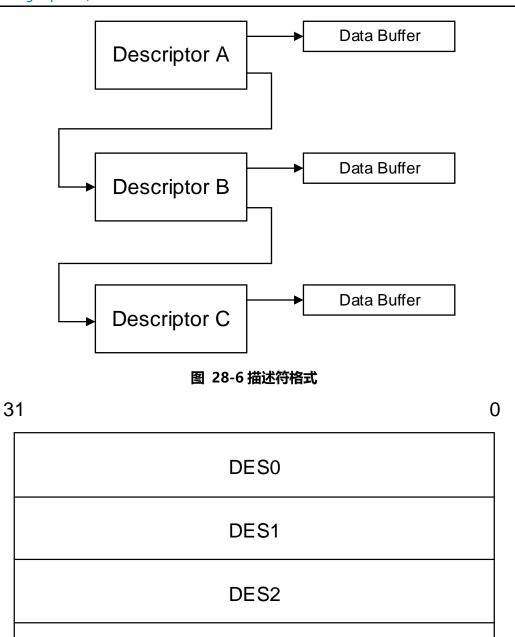

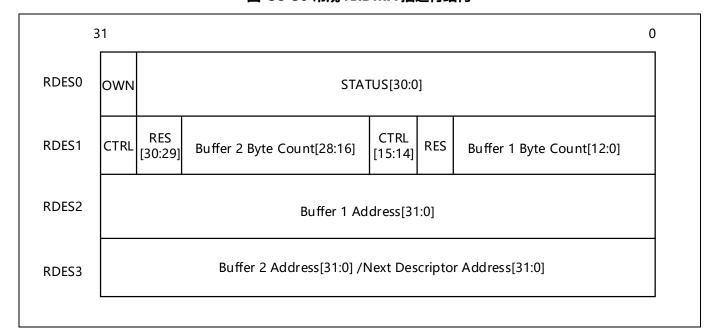

|     | 28.4.4. IDMAC                                    | 570 |

|     | 28.5. SDMMC 寄存器描述                                | 575 |

|     | 28.5.1. 寄存器列表                                    | 575 |

|     | 28.5.2. 控制寄存器(SDMMC_CTRL: 00h)                   | 576 |

|     | 28.5.3. 电源使能寄存器(SDMMC_PWREN: 04h)                | 578 |

| 28.5.4. 时钟分频寄存器(SDMMC_CLKDIV: 08h)        | 578         |

|-------------------------------------------|-------------|

| 28.5.5. 时钟源寄存器 (SDMMC_CLKSRC: 0Ch)        | 578         |

| 28.5.6. 时钟使能寄存器 (SDMMC_CLKENA: 10h)       | 579         |

| 28.5.7. 超时寄存器(SDMMC_TMOUT: 14h)           | 579         |

| 28.5.8. 卡类型寄存器(SDMMC_CTYPE: 18h)          | 579         |

| 28.5.9. 块大小寄存器(SDMMC_BLKSIZ: 1Ch)         | 580         |

| 28.5.10. 字节个数寄存器(SDMMC_BYTCNT: 20h)       | 580         |

| 28.5.11. 中断屏蔽寄存器(SDMMC_INTMASK: 24h)      | 580         |

| 28.5.12. 命令参数寄存器(SDMMC_CMDARG: 28h)       | 581         |

| 28.5.13. 命令寄存器(SDMMC_CMD: 2Ch)            | 581         |

| 28.5.14. 响应 0 寄存器(SDMMC_RESP0: 30h)       | 583         |

| 28.5.15. 响应 1 寄存器(SDMMC_RESP1: 34h)       | 583         |

| 28.5.16. 响应 2 寄存器(SDMMC_RESP2: 38h)       | 583         |

| 28.5.17. 响应 3 寄存器(SDMMC_RESP3: 3Ch)       | 584         |

| 28.5.18. 屏蔽中断状态寄存器(SDMMC_MINTSTS: 40h)    | 584         |

| 28.5.19. 原始中断状态寄存器(SDMMC_RINTSTS: 44h).   | 584         |

| 28.5.20. 状态寄存器(SDMMC_STATUS: 48h)         | 585         |

| 28.5.21. FIFO 阈值寄存器(SDMMC_FIFOTH: 4Ch)    | 586         |

| 28.5.22. 转移的卡字节计数寄存器(SDMMC_TCBCNT: 50     | Ch)587      |

| 28.5.23. 转移的 FIFO 字节计数寄存器(SDMMC_TBBCN     | T: 60h)587  |

| 28.5.24. 去抖动寄存器(SDMMC_DEBNCE: 64h)        | 587         |

| 28.5.25. UHS 寄存器(SDMMC_UHS_REG: 74h)      | 587         |

| 28.5.26. 硬件复位寄存器(SDMMC_RSTN: 78h)         | 588         |

| 28.5.27. 总线模式寄存器(SDMMC_BMOD: 80h)         | 588         |

| 28.5.28. 轮询需求寄存器(SDMMC_PLDMND: 84h)       | 589         |

| 28.5.29. 描述符列表基地址寄存器(SDMMC_DBADDR: 8      | 38h)589     |

| 28.5.30. IDMA 状态寄存器(SDMMC_IDSTS: 8Ch)     | 589         |

| 28.5.31. IDMA 中断使能寄存器(SDMMC_IDINTEN: 90h  | )591        |

| 28.5.32. 当前主机描述符地址寄存器(SDMMC_DSCADD        | R: 94h) 592 |

| 28.5.33. 当前缓冲区地址寄存器(SDMMC_BUFADDR: 98     | 3h)592      |

| 28.5.34. 卡阈值控制寄存器(SDMMC_CTHCTL: 100h)     | 592         |

| 28.5.35. EMMC DDR 寄存器(SDMMC_EMMC_DDR: 10  | Ch)592      |

| 28.5.36. 相位移动寄存器(SDMMC_ENA_SHIFT: 110h)   | 593         |

| 28.5.37. FIFO 通道访问寄存器(SDMMC_DATA: 200Ch). | 593         |

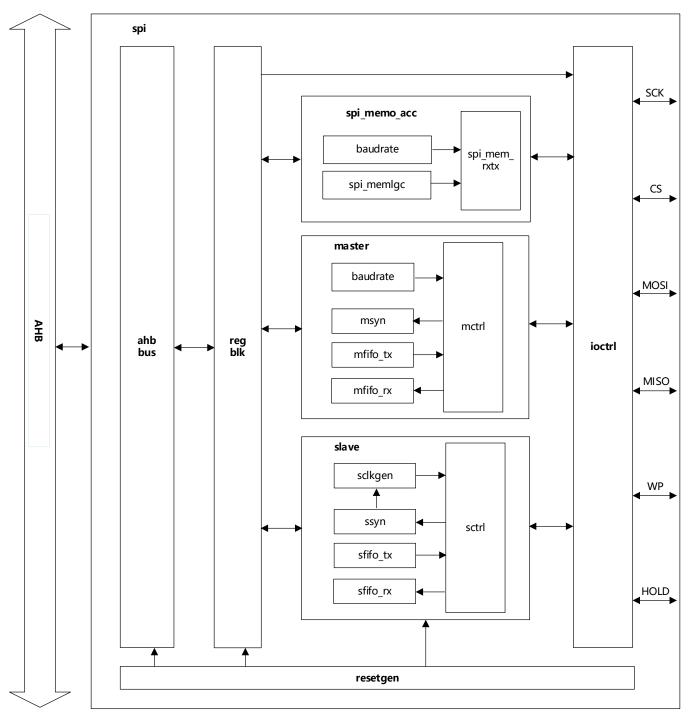

| 29. 串行外设接口 (SPI)                          |             |

| 29.1. 概述                                  | 594         |

| 29.2. 要特性                                 | 592         |

| 29.3. 功能描述                       | 595 |

|----------------------------------|-----|

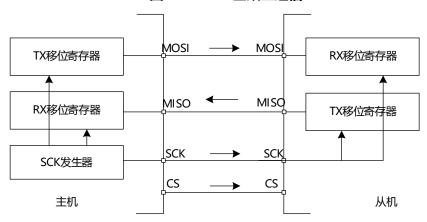

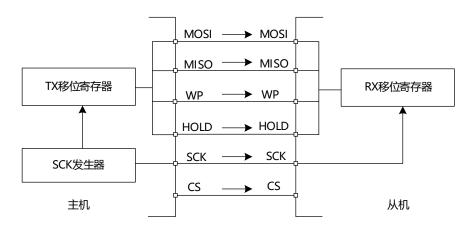

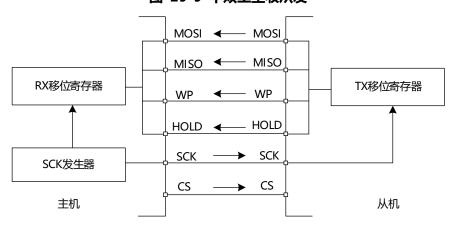

| 29.3.1. 结构框图                     | 595 |

| 29.3.2. SPI 的功能模式                | 595 |

| 29.3.3. SPI 接口信号                 | 596 |

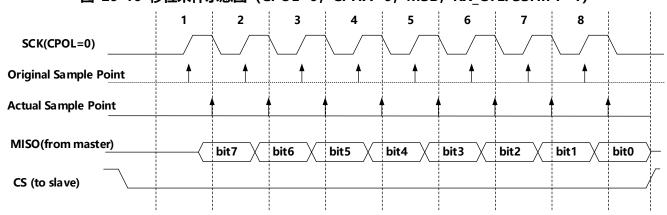

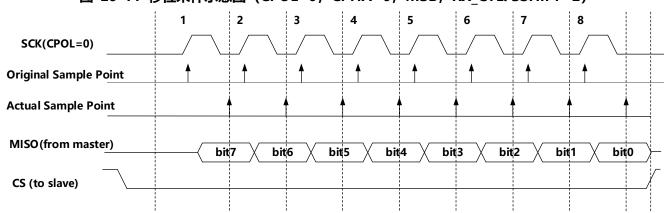

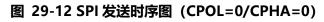

| 29.3.4. SPI 通信格式                 | 596 |

| 29.3.5. SCK 波特率设置                | 597 |

| 29.3.6. 接口模式                     | 597 |

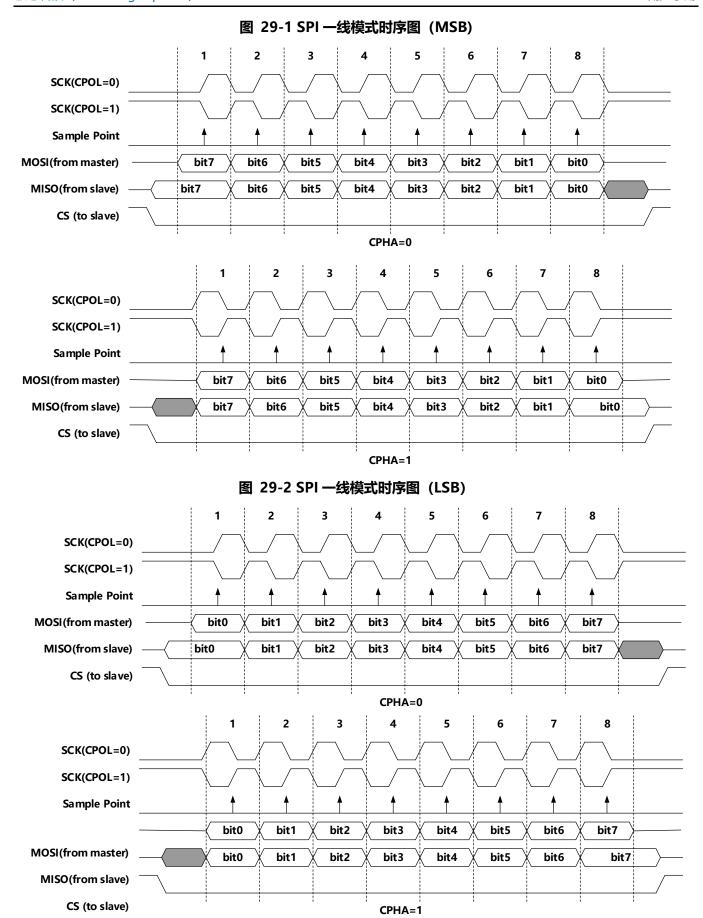

| 29.3.7. 1 线模式                    | 597 |

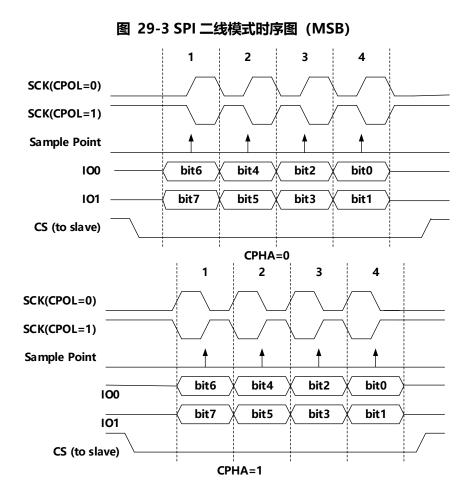

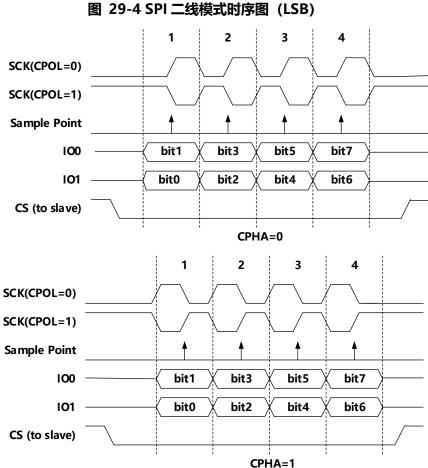

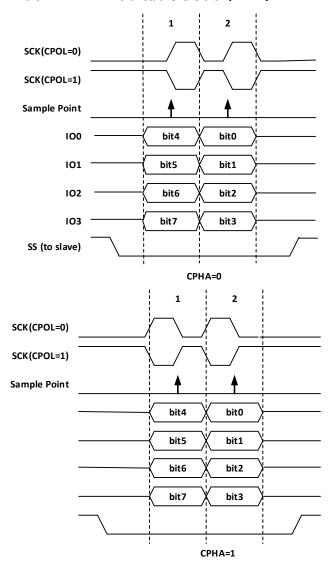

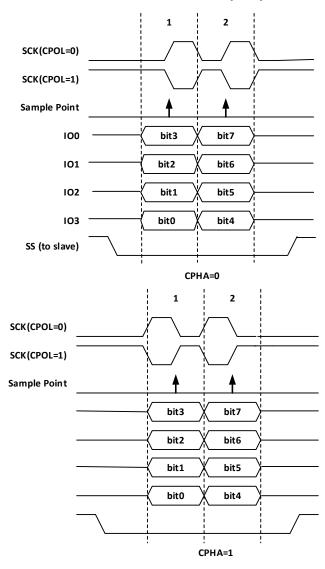

| 29.3.8. 2 线模式                    | 598 |

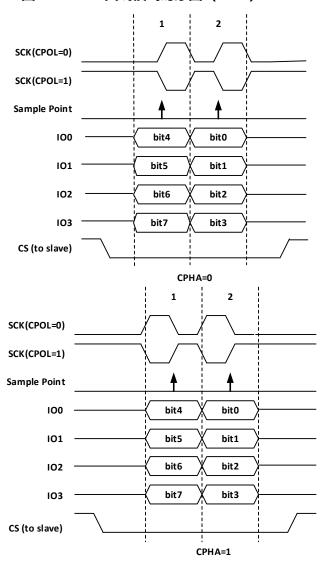

| 29.3.9. 4 线模式                    | 600 |

| 29.3.10. 通信类型                    | 602 |

| 29.3.11. SPI 多片选功能               | 604 |

| 29.3.12. SPI 从机 NCS 功能           | 604 |

| 29.3.13. 采样移位                    | 604 |

| 29.3.14. SPI 从机滤毛刺功能             | 605 |

| 29.3.15. 传输等待功能                  | 605 |

| 29.3.16. 批量传输                    | 606 |

| 29.3.17. SPI 中断和状态               | 606 |

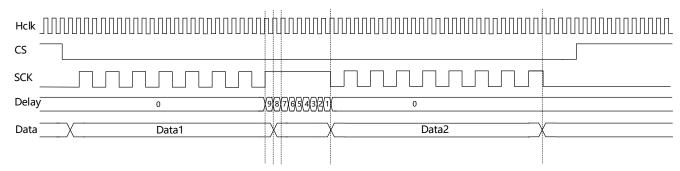

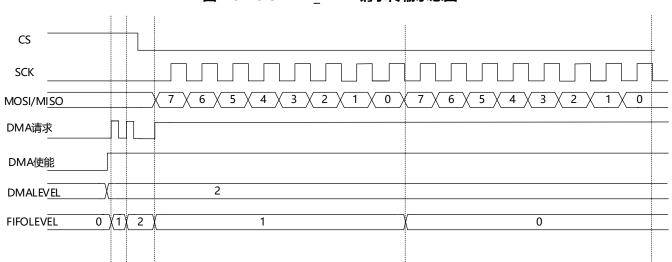

| 29.3.18. SPI 的 DMA 传输            | 607 |

| 29.3.19. SPI Dummy 字节            | 608 |

| 29.3.20. SPI 访问存储器命令序列           | 608 |

| 29.3.21. 内存映射模式                  | 610 |

| 29.4. 配置流程                       | 612 |

| 29.4.1. SPI 主模式发送                | 612 |

| 29.4.2. SPI 主模式接收                | 612 |

| 29.4.3. SPI 从模式发送                | 613 |

| 29.4.4. SPI 从模式接受                | 613 |

| 29.4.5. SPI 存储器内存映射模式读写          | 614 |

| 29.5. SPI 寄存器描述                  | 614 |

| 29.5.1. 寄存器列表                    | 614 |

| 29.5.2. 数据寄存器(SPI_DAT: 00h)      | 615 |

| 29.5.3. 波特率设置寄存器(SPI_BAUD: 04h)  | 615 |

| 29.5.4. 控制寄存器(SPI_CTL: 08h)      | 615 |

| 29.5.5. 发送控制寄存器(SPI_TX_CTL: 0Ch) | 616 |

| 29.5.6. 接收控制寄存器(SPI_RX_CTL: 10h) | 617 |

| 29.5.7. 中断控制寄存器(SPI_IE: 14h)     | 618 |

| 29.5.8. 状态寄存器(SPI_STATUS: 18h)   | 620 |

|     | 29.5.9. 发送等待寄存器(SPI_TXDelay: 1Ch)           | 621 |

|-----|---------------------------------------------|-----|

|     | 29.5.10. 批量传输数据个数寄存器(SPI_BATCH : 20h)       | 621 |

|     | 29.5.11. 从设备选择寄存器(SPI_CS: 24h)              | 622 |

|     | 29.5.12. 管脚输出方向(SPI_OUT_EN: 28h)            | 622 |

|     | 29.5.13. SPI 取值控制寄存器(SPI_MEMO_ACC: 2Ch)     | 623 |

|     | 29.5.14. SPI 取值命令寄存器(SPI_CMD: 30h)          | 624 |

|     | 29.5.15. SPI 取值交替字节寄存器(SPI_ALTER_BYTE: 34h) | 624 |

|     | 29.5.16. CS 低超时计数值(SPI_CS_TOUT_VAL: 38h)    | 625 |

| 30. | . 八线 SPI 接口 (OSPI)                          | 626 |

|     | 30.1. 概述                                    | 626 |

|     | 30.2. 主要特性                                  | 626 |

|     | 30.3. 功能描述                                  | 627 |

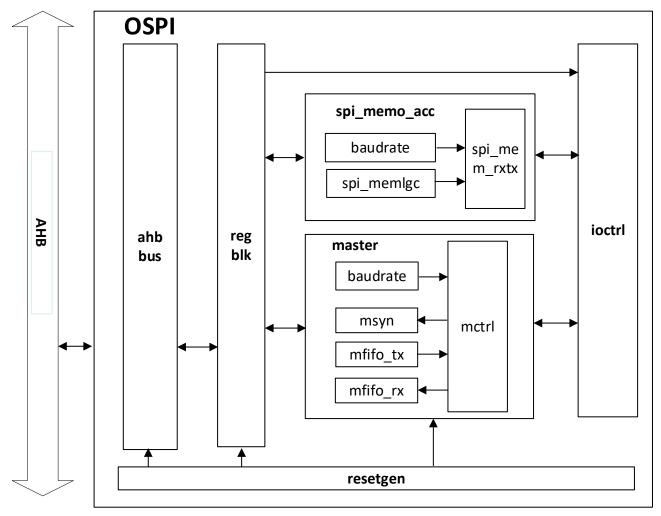

|     | 30.3.1. 结构框图                                | 627 |

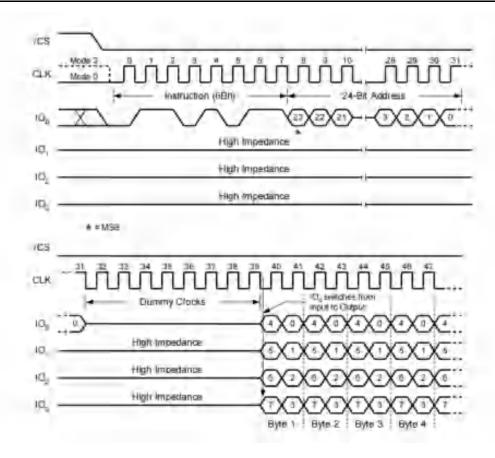

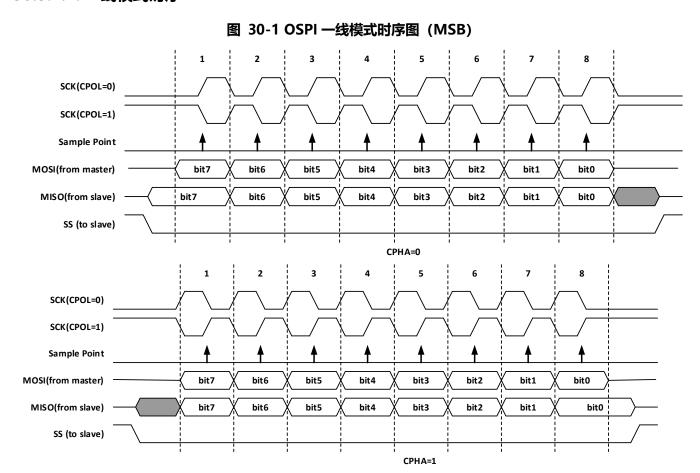

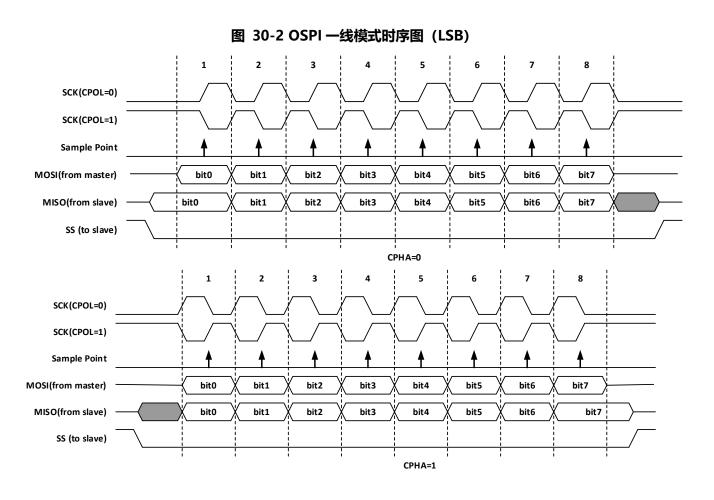

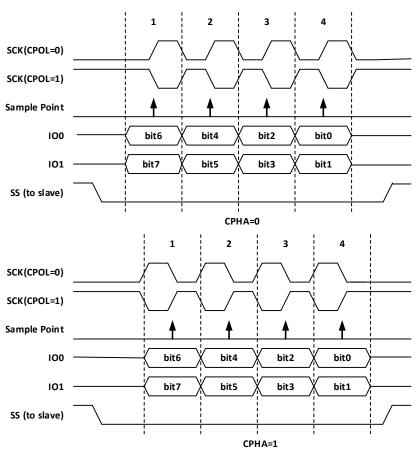

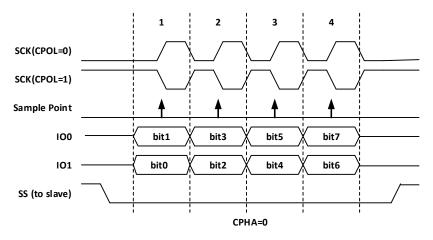

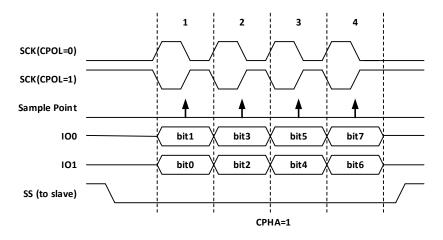

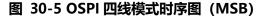

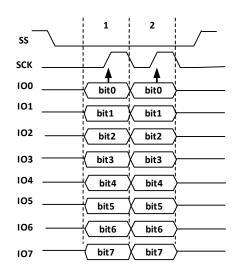

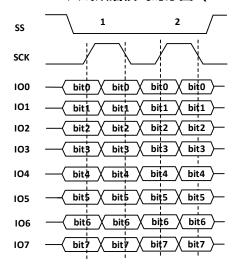

|     | 30.3.2. 时序图                                 | 627 |

|     | 30.3.3. 时钟波特率设置                             | 632 |

|     | 30.3.4. DMA 请求                              | 632 |

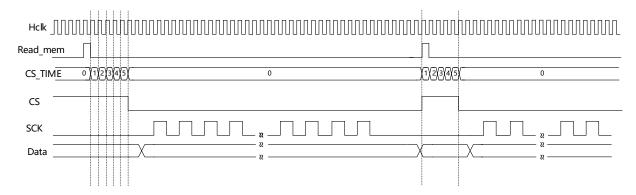

|     | 30.3.5. 存储器读取模式                             | 632 |

|     | 30.4. 配置流程                                  | 633 |

|     | 30.4.1. OSPI 主模式发送                          | 633 |

|     | 30.4.2. OSPI 主模式接收                          | 634 |

|     | 30.4.3. OSPI 主模式接收时 Dummy 控制位               | 635 |

|     | 30.4.4. OSPI 存储器读取                          | 635 |

|     | 30.4.5. OSPI 存储器读取 (连读)                     | 635 |

|     | 30.4.6. OSPI SRAM 写入                        | 636 |

|     | 30.5. OSPI 寄存器描述                            | 636 |

|     | 30.5.1. 寄存器列表                               | 636 |

|     | 30.5.2. 发送数据寄存器(OSPI_TX_DAT: 00h)           | 637 |

|     | 30.5.3. 接收数据寄存器(OSPI_RX_DAT: 00h)           | 637 |

|     | 30.5.4. 波特率设置寄存器(OSPI_BAUD: 04h)            | 637 |

|     | 30.5.5. 控制寄存器(OSPI_CTL: 08h)                | 638 |

|     | 30.5.6. 发送控制寄存器(OSPI_TX_CTL: 0Ch)           | 640 |

|     | 30.5.7. 接收控制寄存器(OSPI_RX_CTL: 10h)           | 640 |

|     | 30.5.8. 中断控制寄存器(OSPI_IE: 14h)               | 643 |

|     | 30.5.9. 状态寄存器(OSPI_STATUS: 18h)             | 645 |

|     | 30.5.10. 发送等待寄存器(OSPI_TXDelay: 1Ch)         | 647 |

|     | 30.5.11. 批量传输数据个数寄存器(OSPI_BATCH: 20h)       | 647 |

|     | 30.5.12. 从设备选择寄存器(OSPI CS: 24h)             | 647 |

|     | 30.5.13. 管脚输出方向(OSPI_OUT_EN: 28h)         | 648 |

|-----|-------------------------------------------|-----|

|     | 30.5.14. 取值控制寄存器 1(OSPI_MEMO_ACC1: 2Ch)   | 649 |

|     | 30.5.15. 取值命令寄存器(OSPI_CMD: 30h)           | 651 |

|     | 30.5.16. 取值交替字节寄存器(OSPI_ALTER_BYTE: 34h)  | 651 |

|     | 30.5.17. CS 低超时计数值(OSPI_CS_TOUT_VAL: 38h) | 651 |

|     | 30.5.18. 取值控制寄存器 2(OSPI_MEMO_ACC2: 3Ch)   | 652 |

| 31. | . 通用异步收发器 (UART)                          | 654 |

|     | 31.1. 概述                                  | 654 |

|     | 31.2. 主要特性                                | 654 |

|     | 31.2.1. UART 的基本功能特性                      | 654 |

|     | 31.2.2. UART 的扩展功能特性                      | 654 |

|     | 31.3. 功能描述                                | 655 |

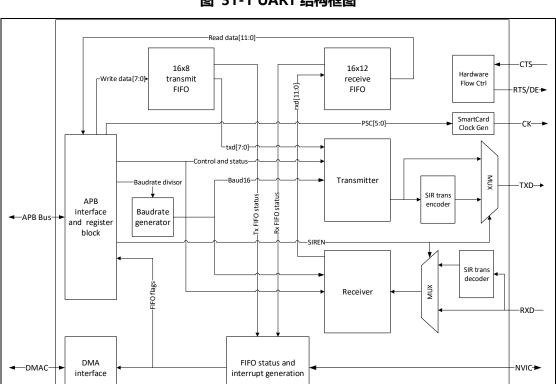

|     | 31.3.1. 结构框图                              | 655 |

|     | 31.3.2. UART 信号                           | 655 |

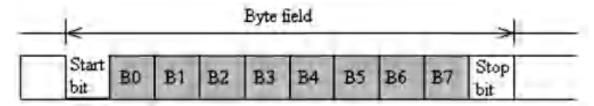

|     | 31.3.3. UART 帧字符结构                        | 656 |

|     | 31.3.4. UART FIFO 及触发阈值                   | 656 |

|     | 31.3.5. UART 波特率                          | 656 |

|     | 31.3.6. 串口设置                              | 656 |

|     | 31.3.7. 总线空闲(IDLEI)检测                     | 656 |

|     | 31.3.8. UART 数据发送                         | 657 |

|     | 31.3.9. UART 数据接收                         | 657 |

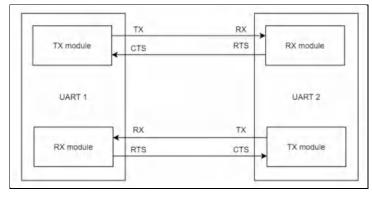

|     | 31.3.10. CTS 和 RTS 流控功能                   | 657 |

|     | 31.3.11. 通过 DMA 进行 UART 数据收发              | 657 |

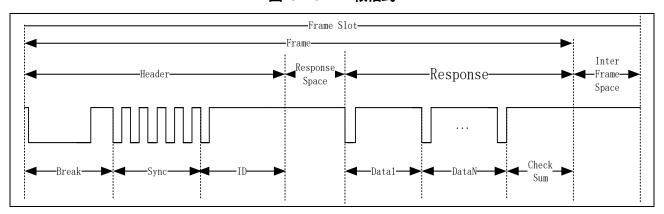

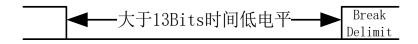

|     | 31.3.12. LIN 总线功能                         | 658 |

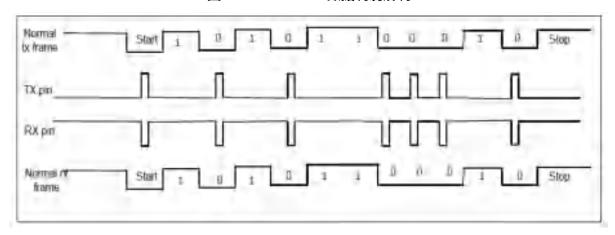

|     | 31.3.13. IrDA SIR 功能                      | 658 |

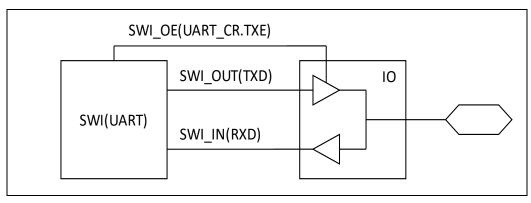

|     | 31.3.14. 单线半双工通信                          | 659 |

|     | 31.3.15. 智能卡主模式                           | 659 |

|     | 31.3.16. 多机通信                             | 660 |

|     | 31.3.17. 波特率自适应                           | 661 |

|     | 31.3.18. RS485 的控制器支持                     | 661 |

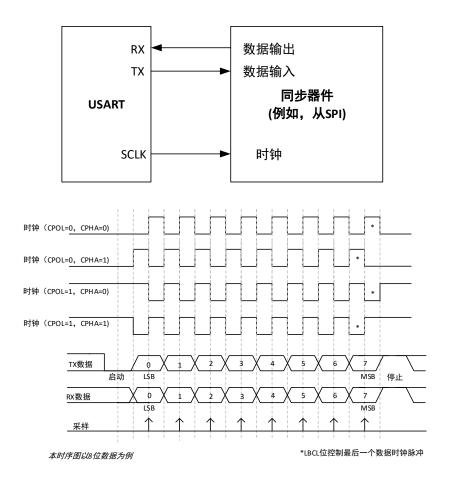

|     | 31.3.19. 同步模式                             | 661 |

|     | 31.4. UART 中断                             | 662 |

|     | 31.5. 配置流程                                | 663 |

|     | 31.5.1. 串口设置                              | 663 |

|     | 31.5.2. 串口的发送和接收                          | 663 |

|     | 31.5.3. LIN 硬件功能支持                        | 663 |

|     | 31.5.4. IrDA SIR 功能使用流程                   | 664 |

| 31.5.5. 单线模式功能使用流程                   | 664 |

|--------------------------------------|-----|

| 31.5.6. 智能卡功能使用流程                    | 664 |

| 31.5.7. 多机通信功能使用流程                   | 664 |

| 31.5.8. 波特率自适应功能使用流程                 | 664 |

| 31.5.9. RS485 的 DE 控制功能使用流程          | 665 |

| 31.5.10. 同步模式                        | 665 |

| 31.6. UART 寄存器描述                     | 665 |

| 31.6.1. 寄存器列表                        | 665 |

| 31.6.2. 数据寄存器(UART_DR: 00h)          | 666 |

| 31.6.3. 标志位寄存器(UART_FR: 04h)         | 666 |

| 31.6.4. 波特率寄存器(UART_BRR: 08h)        | 668 |

| 31.6.5. 中断使能寄存器(UART_IE: 0Ch)        | 668 |

| 31.6.6. 中断和状态寄存器(UART_ISR: 10h)      | 669 |

| 31.6.7. 控制寄存器 1(UART_CR1: 14h)       | 671 |

| 31.6.8. 控制寄存器 2(UART_CR2: 18h)       | 672 |

| 31.6.9. 控制寄存器 3(UART_CR3: 1Ch)       | 673 |

| 31.6.10. 保护时间和预分频寄存器(UART_GTPR: 20h) | 674 |

| 31.6.11. 比特计时寄存器(UART_BCNT: 24h)     | 675 |

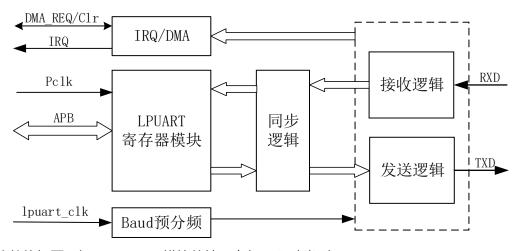

| 32. 低功耗串口(LPUART)                    | 676 |

| 32.1. 概述                             | 676 |

| 32.2. 主要特性                           | 676 |

| 32.3. LPUART 功能描述                    | 676 |

| 32.3.1. 时钟                           | 677 |

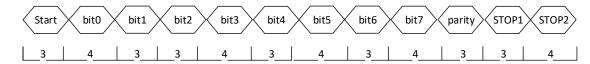

| 32.3.2. 波特率                          | 677 |

| 32.3.3. 数据位                          | 678 |

| 32.3.4. 校验位                          | 678 |

| 32.3.5. 停止位                          | 678 |

| 32.3.6. 数据极性                         | 678 |

| 32.3.7. 地址                           | 678 |

| 32.3.8. STOP 唤醒                      | 678 |

| 32.3.9. DMA 请求                       | 679 |

| 32.3.10. 中断                          | 679 |

| 32.4. 配置流程                           | 680 |

| 32.4.1. 初始化                          | 680 |

| 32.4.2. 发送                           | 680 |

| 32.4.3. 接收                           | 680 |

| 32.5. LPUART 寄存器描述                   | 681 |

| 32.5.1. 寄存器列表                      | 681 |

|------------------------------------|-----|

| 32.5.2. 接收数据寄存器(LPUART_RXDR: 00h)  | 681 |

| 32.5.3. 发送数据寄存器(LPUART_TXDR: 04h)  | 681 |

| 32.5.4. 线控寄存器(LPUART_LCR: 08h)     | 681 |

| 32.5.5. 控制寄存器(LPUART_CR: 0Ch)      | 682 |

| 32.5.6. 波特率整数部分(LPUART_IBAUD: 10h) | 683 |

| 32.5.7. 波特率小数部分(LPUART_FBAUD: 14h) | 683 |

| 32.5.8. 中断使能寄存器(LPUART_IE: 18h)    | 683 |

| 32.5.9. 状态寄存器(LPUART_SR: 1Ch)      | 684 |

| 32.5.10. 地址寄存器(LPUART_ADDR: 20h)   | 685 |

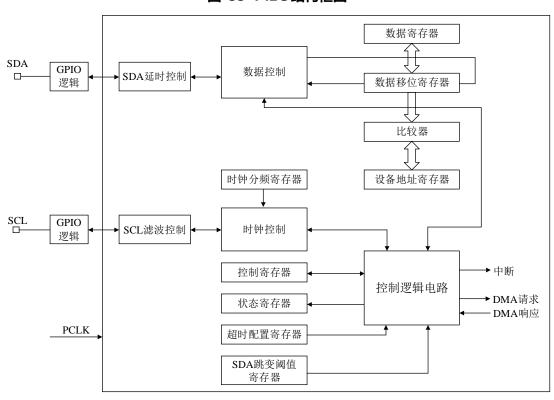

| 33. 内部集成电路总线接口 (I2C)               | 686 |

| 33.1. 概述                           | 686 |

| 33.2. 主要特性                         | 686 |

| 33.3. 结构框图                         | 687 |

| 33.4. 功能描述                         | 687 |

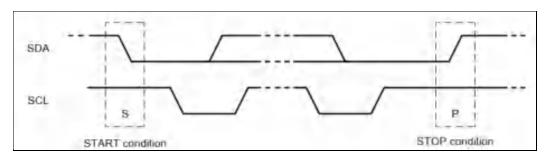

| 33.4.1. 开始和停止条件                    | 687 |

| 33.4.2. 模式选择                       | 687 |

| 33.4.3. 从机地址 SLAVE_ADDR1/2/3       | 688 |

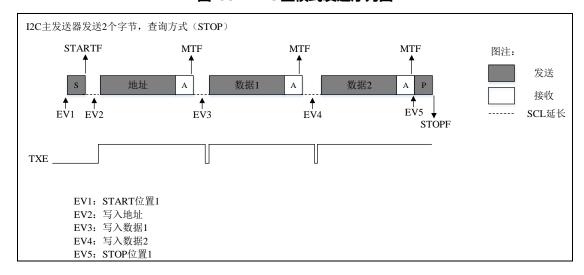

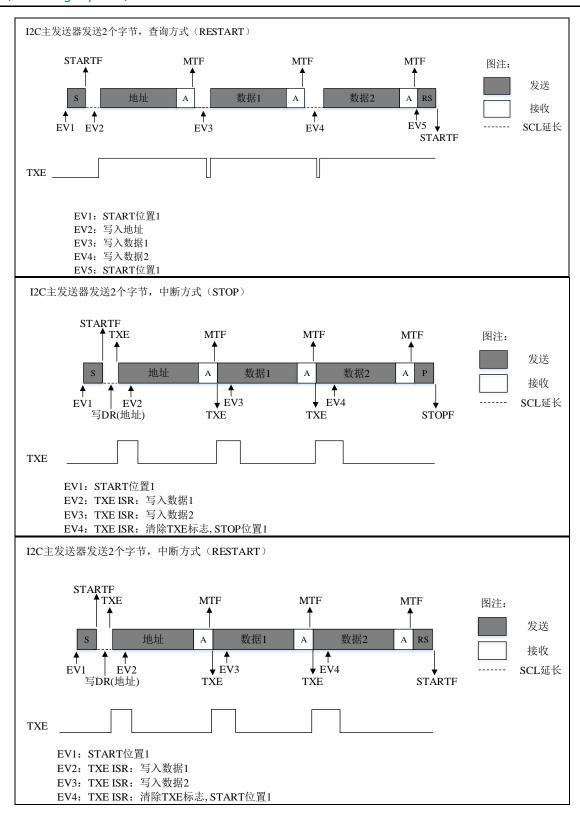

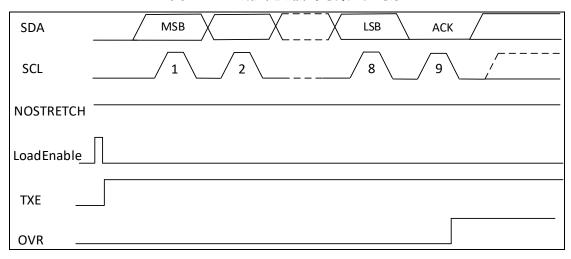

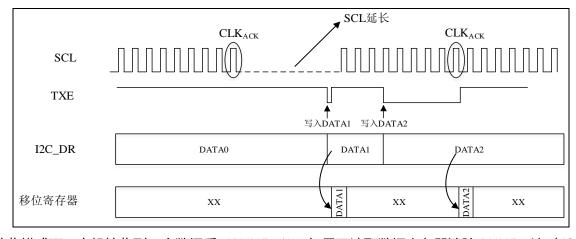

| 33.4.4. 主模式发送                      | 688 |

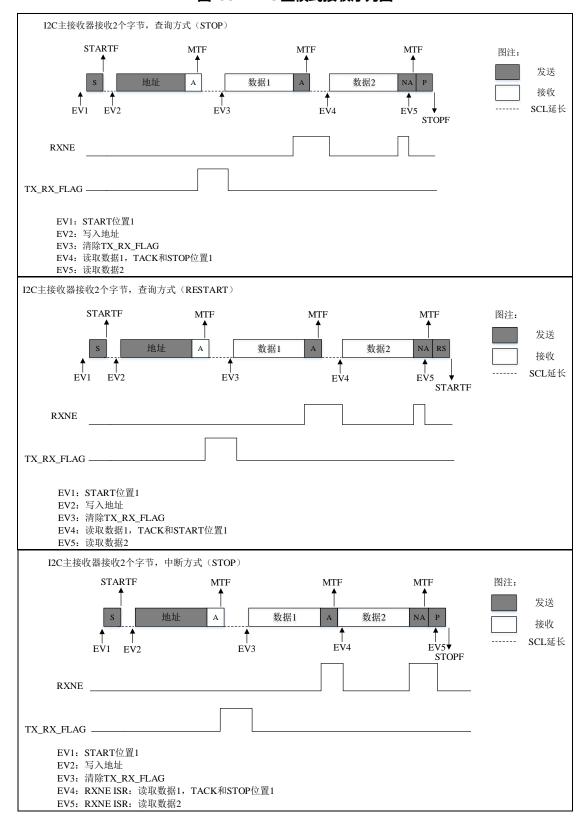

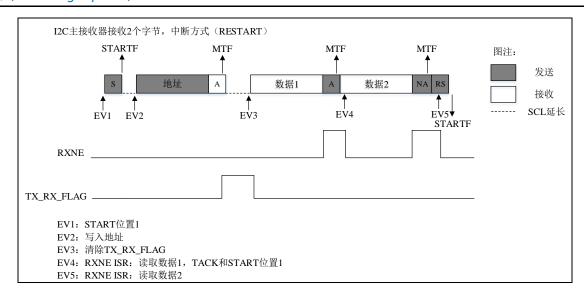

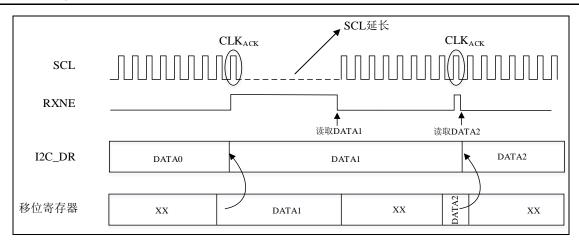

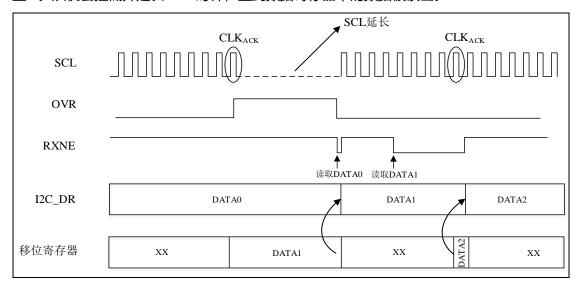

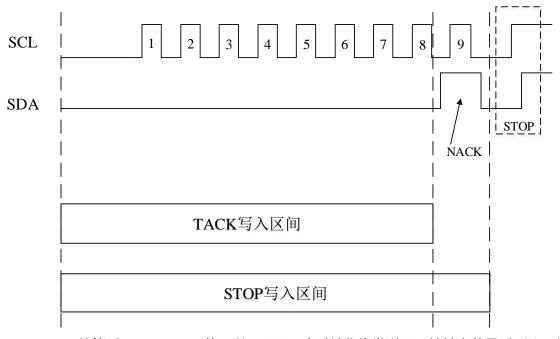

| 33.4.5. 主模式接收                      | 691 |

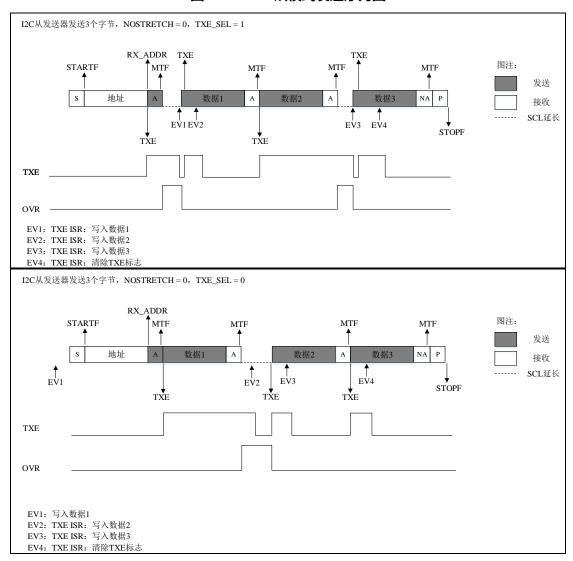

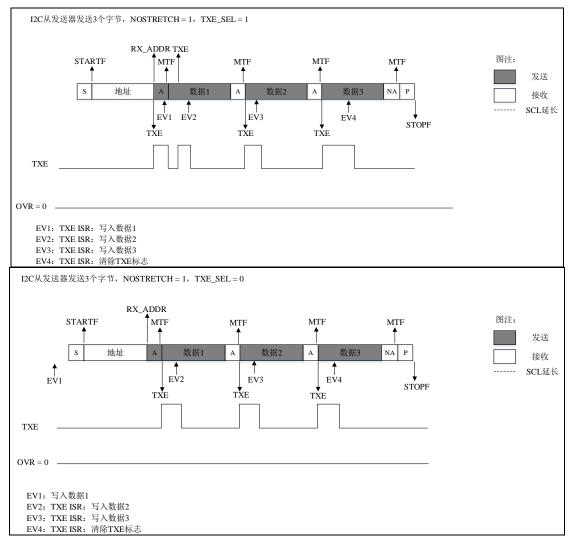

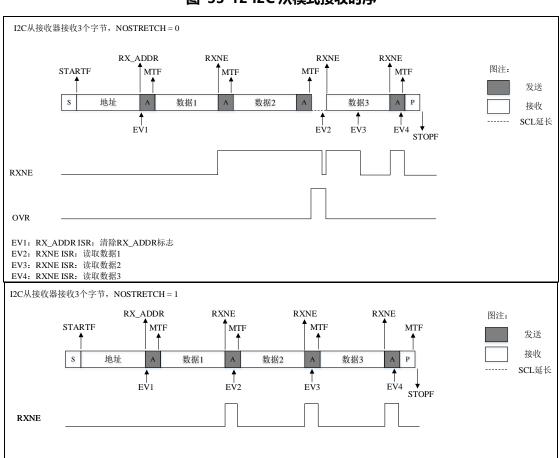

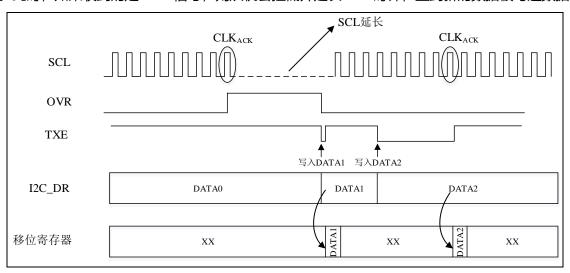

| 33.4.6. 从模式发送                      | 692 |

| 33.4.7. 从模式接收                      | 695 |

| 33.4.8. 时钟 SCL 延长                  | 695 |

| 33.4.9. 错误条件                       | 696 |

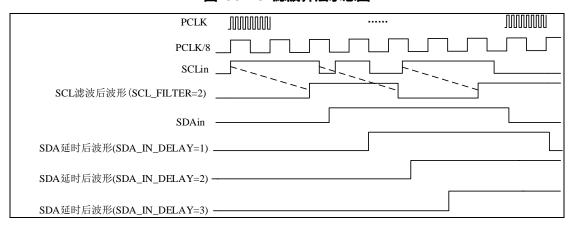

| 33.4.10. SCL 总线滤波算法                | 697 |

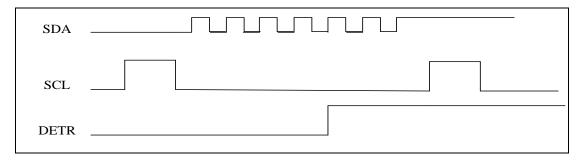

| 33.4.11. SCL 为低时检测 SDA 的跳变         | 698 |

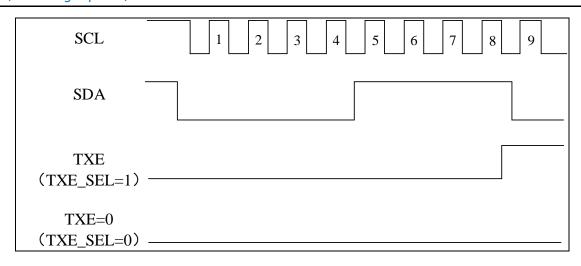

| 33.4.12. TXE_SEL                   | 698 |

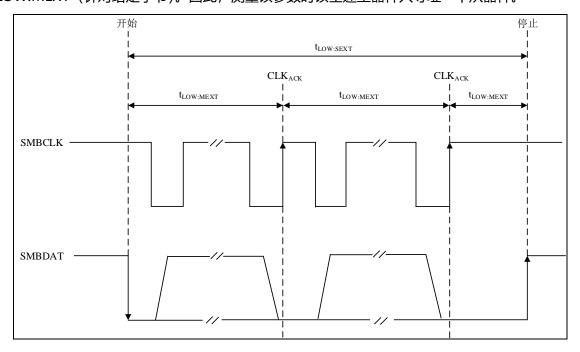

| 33.4.13. SMBus 的功能特性               | 699 |

| 33.4.14. SMBus 初始化                 | 700 |

| 33.4.15. SMBus I2C_TIMEOUT 寄存器配置示例 |     |

| 33.4.16. DMA 请求                    | 701 |

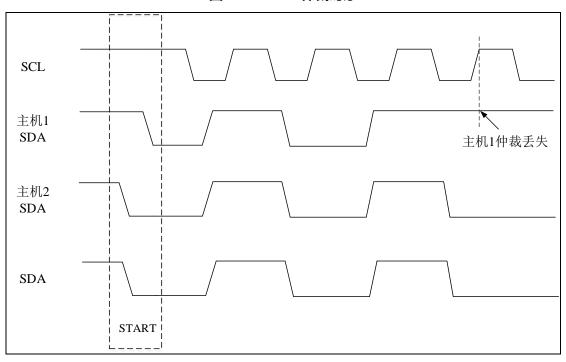

| 33.4.17. I2C 的仲裁机制                 | 702 |

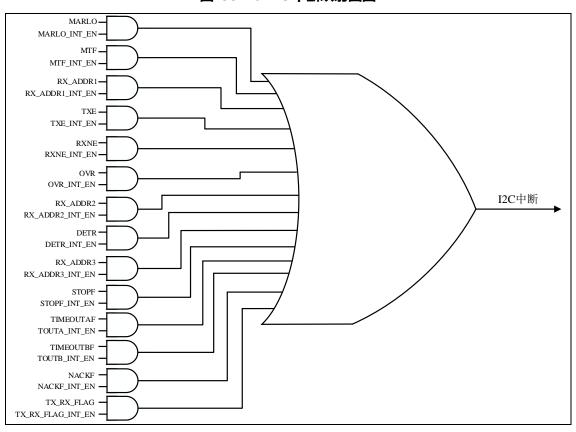

| 33.5. 中断及中断标志                      | 703 |

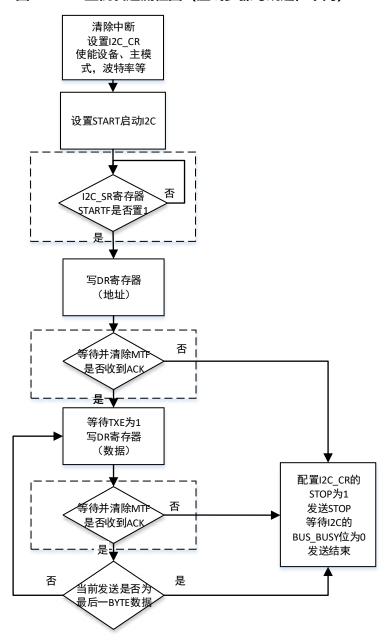

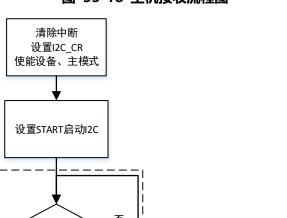

| 33.6. 配置流程                         | 705 |

| 33.6.1. 主发送器                       | 705 |

| 33.6.2. 主接收器                       | 707 |

| 33.6.3. 从发送器                       | 708 |

|     | 33.6.4. 从接收器                                 | 709 |

|-----|----------------------------------------------|-----|

|     | 33.7. I2C 寄存器描述                              | 709 |

|     | 33.7.1. 寄存器列表                                | 709 |

|     | 33.7.2. 设备地址寄存器 1 (I2C_SLAVE_ADDR1: 00h)     | 709 |

|     | 33.7.3. 时钟分频寄存器(I2C_CLK_DIV: 04h)            | 710 |

|     | 33.7.4. 控制寄存器(I2C_CR: 08h)                   | 710 |

|     | 33.7.5. 状态寄存器(I2C_SR: 0Ch)                   | 712 |

|     | 33.7.6. 数据寄存器(I2C_DR: 10h)                   | 714 |

|     | 33.7.7. 设备地址寄存器 2_3 (I2C_SLAVE_ADDR2_3: 14h) | 715 |

|     | 33.7.8. SDA 跳变阈值寄存器 (I2C_DET: 18h)           | 715 |

|     | 33.7.9. 滤波寄存器(I2C_FILTER: 1Ch)               | 715 |

|     | 33.7.10. 超时配置寄存器(I2C_TIMEOUT: 24h)           | 715 |

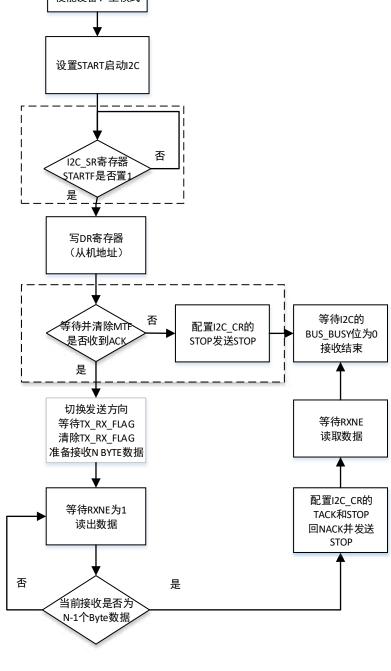

| 34. | . 片上音频接口(I2S)                                | 717 |

|     | 34.1. 概述                                     | 717 |

|     | 34.2. 主要特性                                   | 717 |

|     | 34.3. 结构框图                                   | 717 |

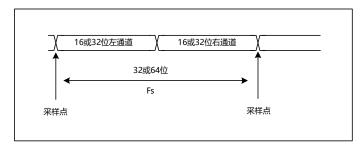

|     | 34.4. 功能描述                                   | 718 |

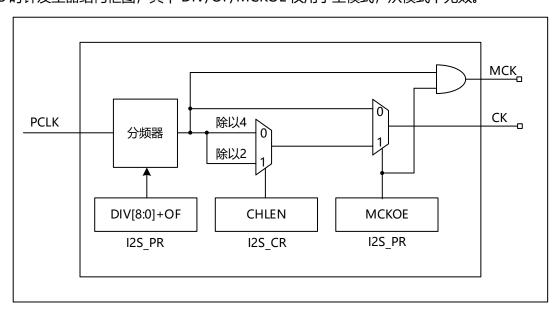

|     | 34.4.1. 时钟                                   | 718 |

|     | 34.4.2. 音频标准                                 | 719 |

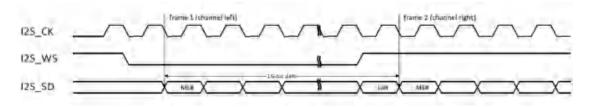

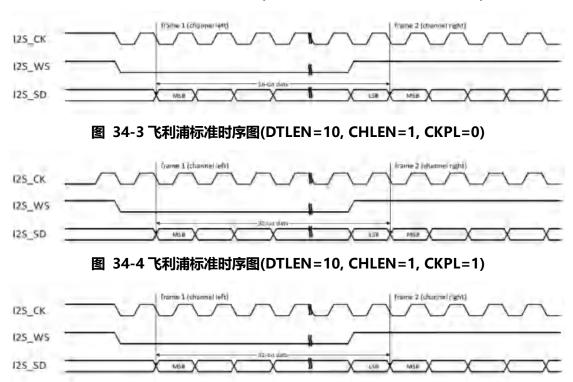

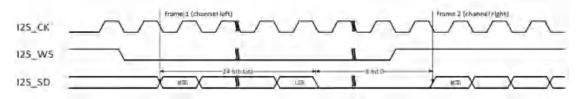

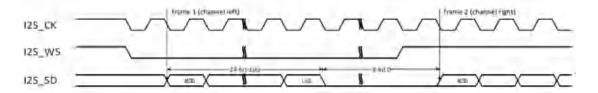

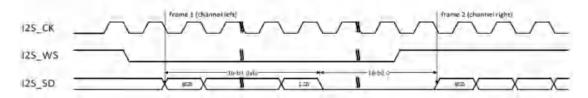

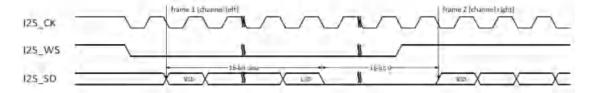

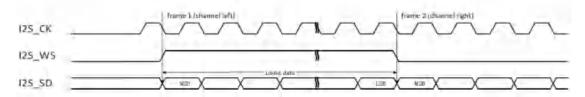

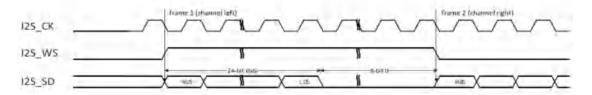

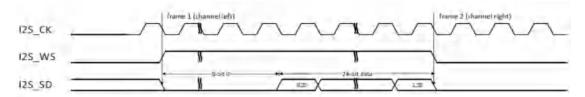

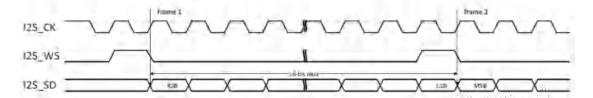

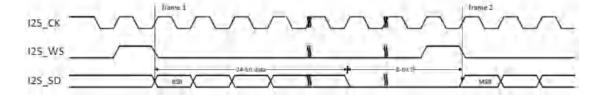

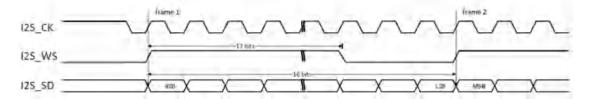

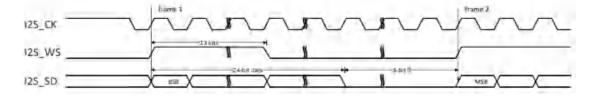

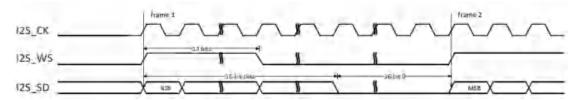

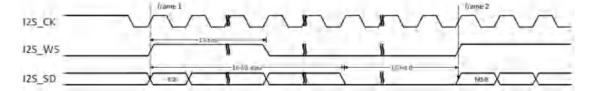

|     | 34.4.3. I2S 飞利浦标准                            | 719 |

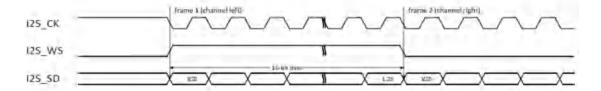

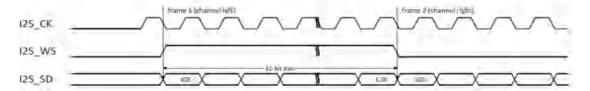

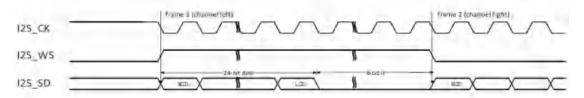

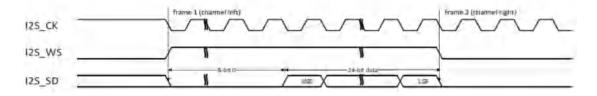

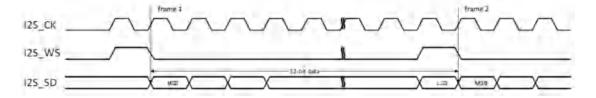

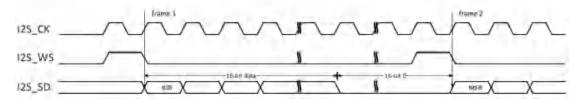

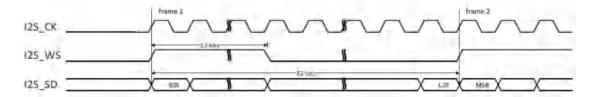

|     | 34.4.4. MSB 对齐标准                             | 721 |

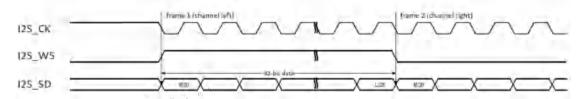

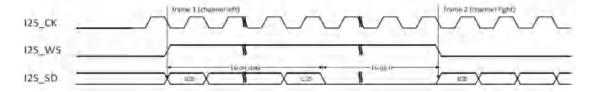

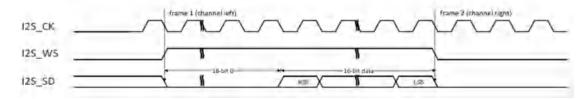

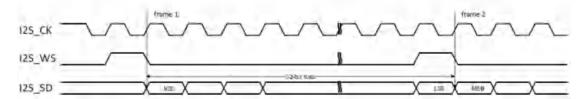

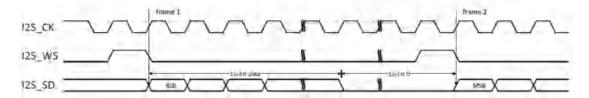

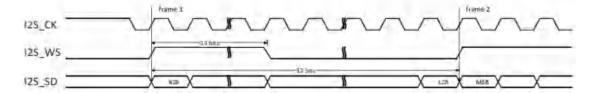

|     | 34.4.5. LSB 对齐标准                             | 722 |

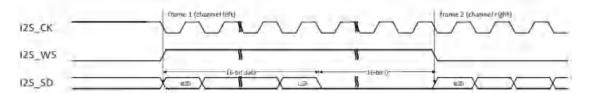

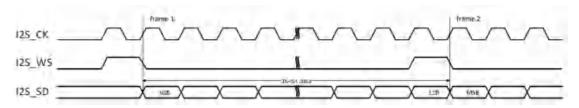

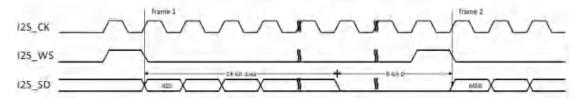

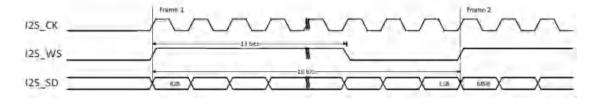

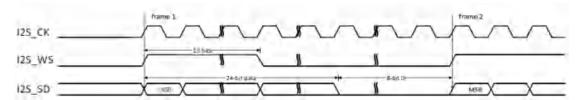

|     | 34.4.6. PCM 对齐标准                             | 723 |

|     | 34.4.7. 运行模式                                 | 726 |

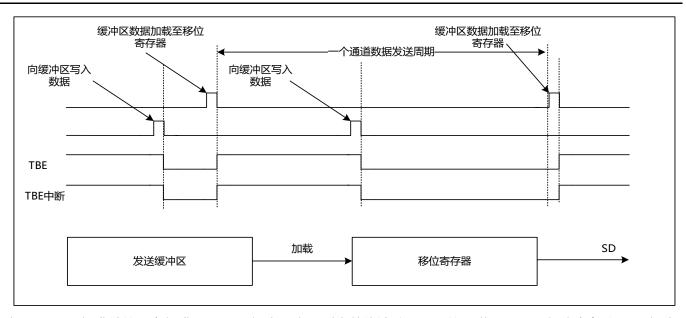

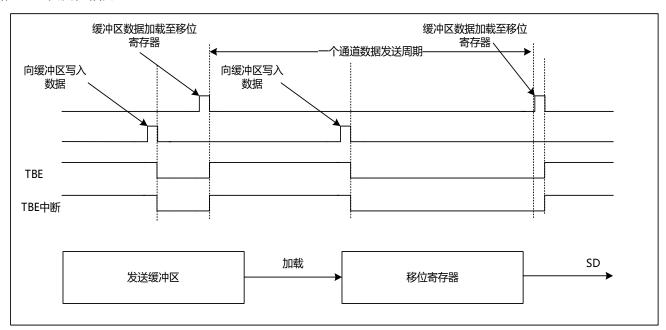

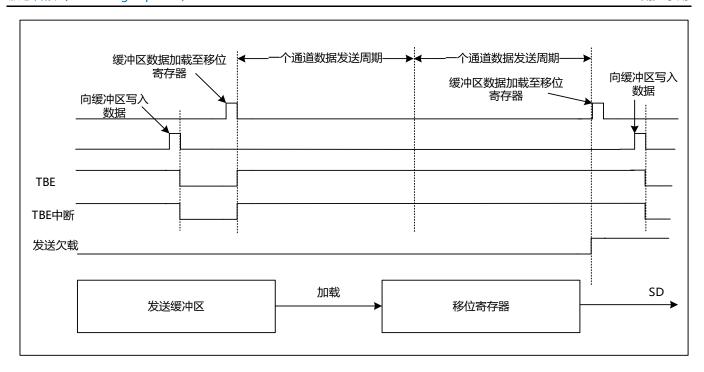

|     | 34.4.8. 主发模式                                 | 726 |

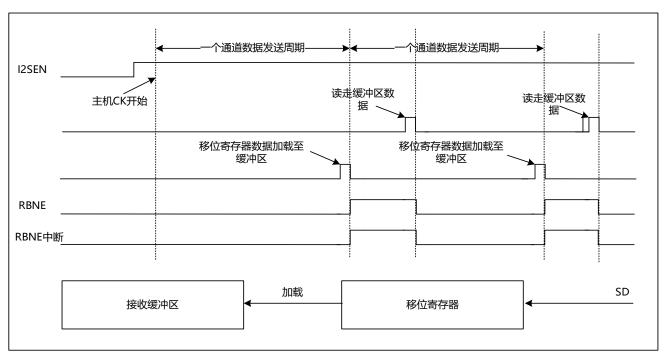

|     | 34.4.9. 主收模式                                 | 727 |

|     | 34.4.10. 从发模式                                | 728 |

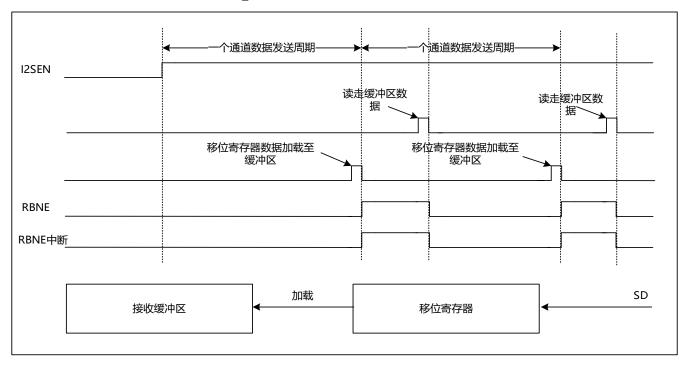

|     | 34.4.11. 从收模式                                | 729 |

|     | 34.4.12. 状态标志                                | 729 |

|     | 34.4.13. 中断                                  | 730 |

|     | 34.4.14. DMA                                 | 730 |

|     | 34.5. 配置流程                                   | 731 |

|     | 34.5.1. 主发模式                                 | 731 |

|     | 34.5.2. 主收模式                                 | 731 |

|     | 34.5.3. 从发模式                                 | 731 |

|     | 34.5.4. 从收模式                                 | 731 |

|     | 34.6. I2S 寄存器描述                              | 732 |

|     | 34.6.1. 寄存器列表                      | 732 |

|-----|------------------------------------|-----|

|     | 34.6.2. 发送数据寄存器(I2S_TXDR: 00h)     | 732 |

|     | 34.6.3. 接收数据寄存器(I2S_RXDR: 04h)     | 732 |

|     | 34.6.4. 控制寄存器(I2S_CR: 08h)         | 732 |

|     | 34.6.5. 时钟预分频寄存器(I2S_PR: 0Ch)      | 734 |

|     | 34.6.6. I2S 中断使能寄存器(I2S_IER: 10h)  | 735 |

|     | 34.6.7. 状态寄存器(I2S_SR: 14h)         | 735 |

|     | 34.6.8. 数据量寄存器 (I2S_RSIZE: 1Ch)    | 736 |

| 35. | . 控制器局域网络(FDCAN)                   | 737 |

|     | 35.1. 概述                           | 737 |

|     | 35.2. 主要特性                         | 737 |

|     | 35.3. 功能描述                         | 738 |

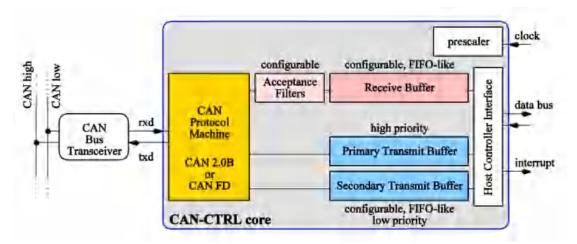

|     | 35.3.1. 结构框图                       | 738 |

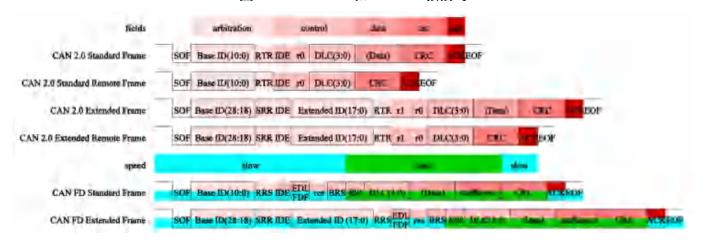

|     | 35.3.2. 帧格式                        | 738 |

|     | 35.3.3. 接受缓冲 RB                    | 739 |

|     | 35.3.4. 发送缓冲 TB                    | 739 |

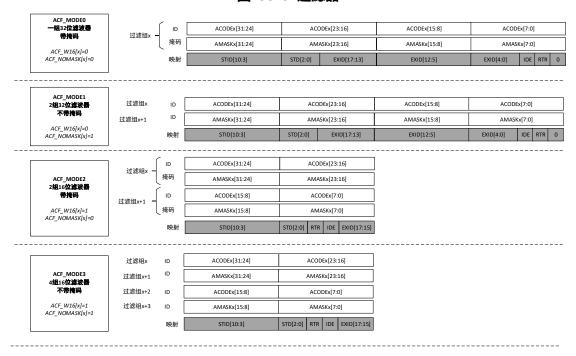

|     | 35.3.5. 过滤器                        | 739 |

|     | 35.3.6. Single Shot 模式             | 740 |

|     | 35.3.7. 取消数据发送                     | 740 |

|     | 35.3.8. 错误处理                       | 741 |

|     | 35.3.9. 节点关闭                       | 741 |

|     | 35.3.10. 仲裁失败位置捕捉                  | 741 |

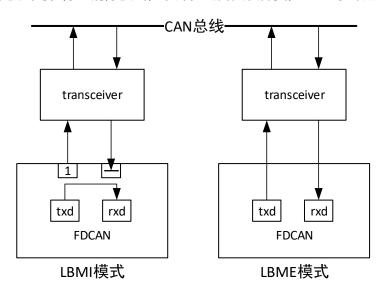

|     | 35.3.11. 回环模式                      | 741 |

|     | 35.3.12. 静默模式                      | 742 |

|     | 35.3.13. AUTOSAR 和 SAE J1939       | 742 |

|     | 35.3.14. Time-Triggered CAN        | 742 |

|     | 35.3.15. CiA 603 Time-Stamping     | 744 |

|     | 35.4. CAN 寄存器描述                    | 746 |

|     | 35.4.1. 寄存器列表                      | 746 |

|     | 35.4.2. 接受缓存(FDCAN_RBUF: 0h)       | 747 |

|     | 35.4.3. 发送缓存(FDCAN_TBUF: 50h)      | 748 |

|     | 35.4.4. 时间戳低位寄存器 (FDCAN_TTSL: 98h) | 749 |

|     | 35.4.5. 时间戳高位寄存器(FDCAN_TTSH: 9Ch)  | 749 |

|     | 35.4.6. 控制寄存器(FDCAN_CR: A0h)       | 749 |

|     | 35.4.7. 中断使能和标志寄存器(FDCAN_IR: A4h)  | 752 |

|     | 35.4.8. 阈值寄存器(FDCAN_LIMIT: A8h)    | 754 |

|     | 35.4.9. 慢位时间寄存器(FDCAN SBTR: ACh)   | 754 |

| 35.4.10. 快位时间寄存器(FDCAN_FBTR: B0h)      | 755 |

|----------------------------------------|-----|

| 35.4.11. 发送延迟补偿寄存器(FDCAN_TDC: B4h)     | 755 |

| 35.4.12. 错误寄存器(FDCAN_ECC: B8h)         | 755 |

| 35.4.13. 过滤组使能寄存器 (FDCAN_ACFCR: BCh)   | 756 |

| 35.4.14. 过滤组模式寄存器 (FDCAN_ACFMODE: C0h) | 756 |

| 35.4.15. 过滤组控制寄存器(FDCAN_ACODR: C4h)    | 757 |

| 35.4.16. 时间戳控制寄存器 (FDCAN_TIMCFG: C8h)  | 757 |

| 35.4.17. TTCAN 配置寄存器(FDCAN_TTCFG: CCh) | 757 |

| 35.4.18. 参考消息寄存器(FDCAN_REFMSG: D0h)    | 758 |

| 35.4.19. 时间控制寄存器(FDCAN_TRIGCFG: D4h)   | 758 |

| 35.4.20. 时间触发寄存器(FDCAN_TTTRIG: D8h)    | 759 |

| 35.4.21. Watch 触发寄存器(FDCAN_WTRIG: DCh) | 759 |

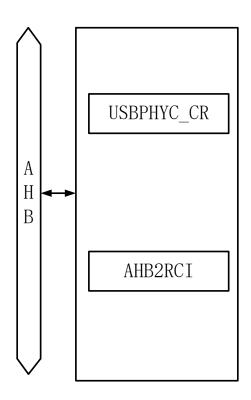

| 36. USBPHY 控制器 (USBPHYC)               | 760 |

| 36.1. 概述                               | 760 |

| 36.2. 主要特性                             | 760 |

| 36.3. 结构框图                             | 760 |

| 36.4. USBPHYC 寄存器描述                    | 760 |

| 36.4.1. 寄存器列表                          | 760 |

| 36.4.2. 调试寄存器 0(USBPHYC_TR0: 00h)      | 761 |

| 36.4.3. 调试寄存器 1(USBPHYC_TR1: 04h)      | 761 |

| 36.4.4. 调试寄存器 2(USBPHYC_TR2: 08h)      | 762 |

| 36.4.5. 调试寄存器 3(USBPHYC_TR3: 0Ch)      | 762 |

| 36.4.6. 控制寄存器(USBPHYC _CR: 80h)        | 763 |

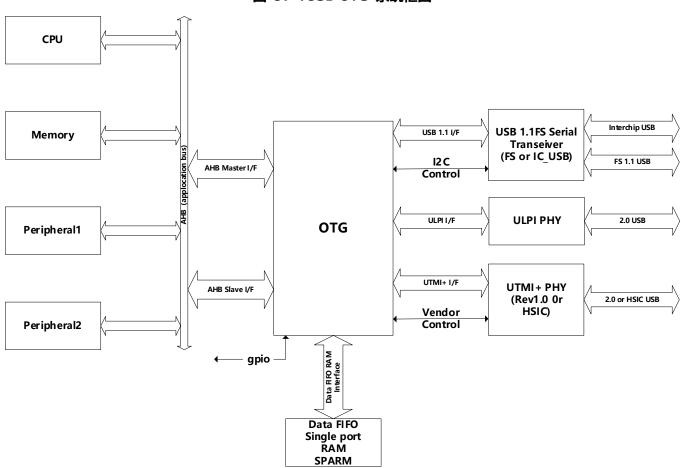

| 37. 高速 USB OTG (OTG_HS)                | 765 |

| 37.1. 概述                               | 765 |

| 37.2. 系统级框图                            | 765 |

| 37.3. 主要特性                             | 765 |

| 37.3.1. 通用特性                           | 765 |

| 37.3.2. 主机模式特性                         | 766 |

| 37.3.3. 从机模式特性                         | 767 |

| 37.4. OTG_HS 功能说明                      | 767 |

| 37.4.1. USB OTG 引脚信号                   | 767 |

| 37.4.2. OTG 模块                         | 767 |

| 37.4.3. 高速 OTG PHY                     | 768 |

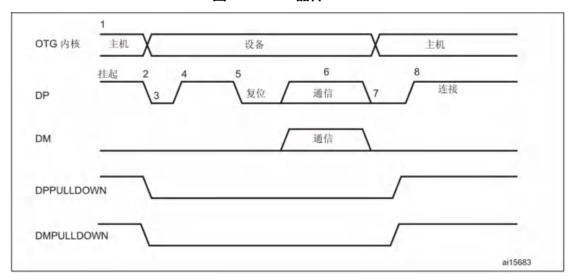

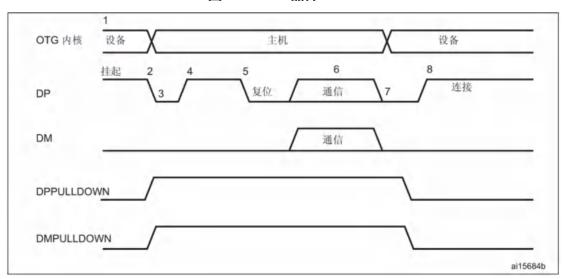

| 37.5. OTG 双角色设备 (DRD)                  | 768 |

| 37.5.1. ID 线检测                         | 768 |

| 37.5.2. HNP 双角色设备                      | 768 |

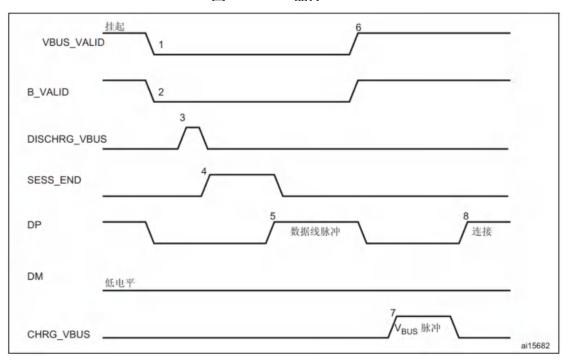

| 37.5.3. SRP 双角色设备         | 768 |

|---------------------------|-----|

| 37.6. USB 从机              | 768 |

| 37.6.1. 支持 SRP 功能的 USB 设备 | 769 |

| 37.6.2. USB 从机状态          | 769 |

| 37.6.3. USB 设备端点          | 769 |

| 37.7. USB 主机              | 771 |

| 37.7.1. 支持 SRP 功能的 USB 主机 | 771 |

| 37.7.2. USB 主机状态          | 771 |

| 37.7.3. 主机通道              | 772 |

| 37.7.4. 主机调度器             | 773 |

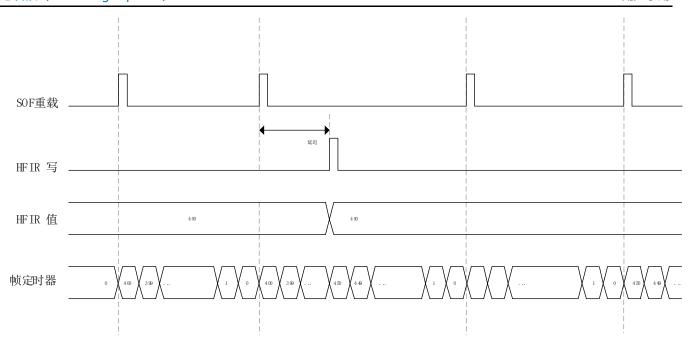

| 37.8. SOF 触发              | 774 |

| 37.8.1. 主机 SOF            | 774 |

| 37.8.2. 设备 SOF            | 774 |

| 37.9. 电源选项                | 775 |

| 37.10. 动态更新 HFIR 寄存器      | 775 |

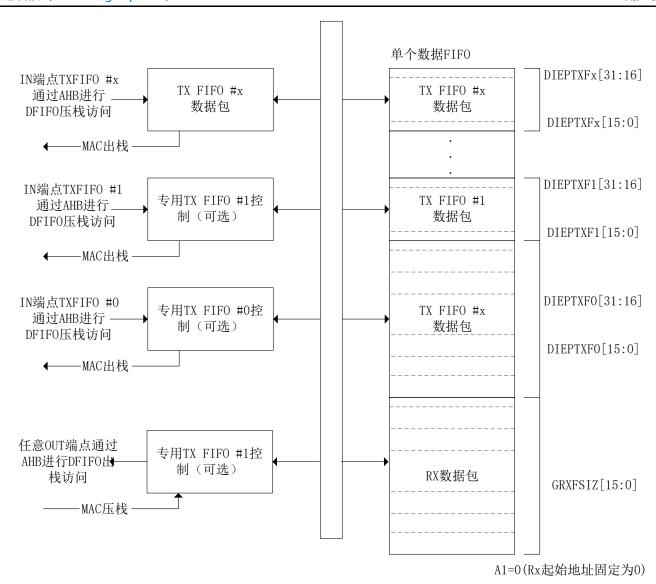

| 37.11. USB 数据 FIFO        | 776 |

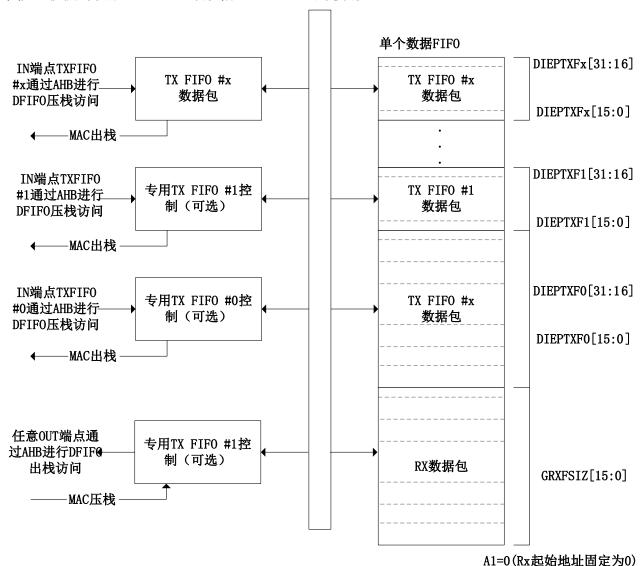

| 37.11.1. 设备 FIFO 架构       | 776 |

| 37.11.2. 主机 FIFO 架构       | 777 |

| 37.11.3. FIFO RAM 分配      | 779 |

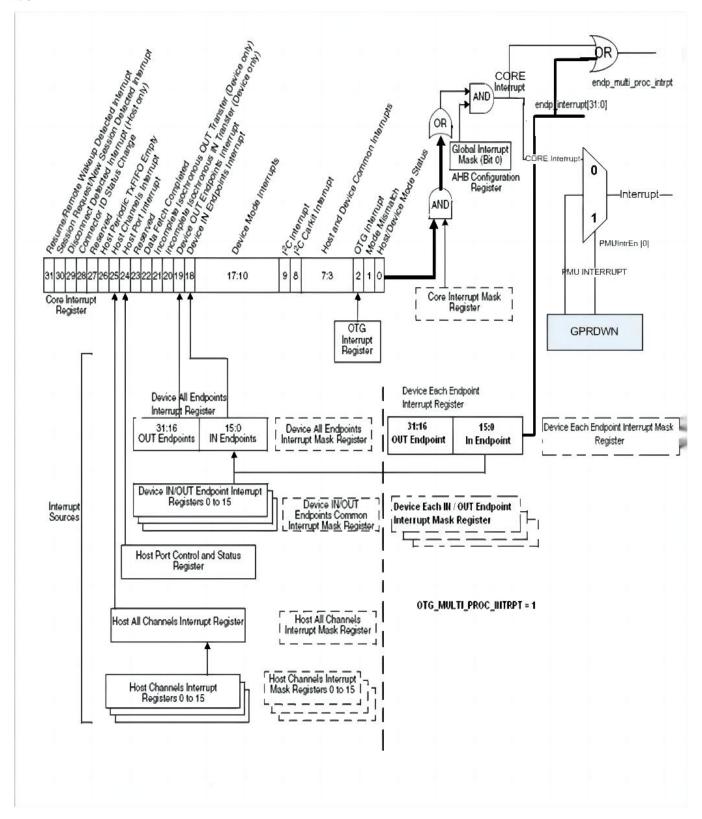

| 37.12. OTG_HS 中断          | 780 |

| 37.13. OTG_HS 控制和状态寄存器    | 781 |

| 37.14. OTG_HS 编程模型        | 781 |

| 37.14.1. 模块初始化            | 781 |

| 37.14.2. 主机初始化            | 782 |

| 37.14.3. 设备初始化            | 782 |

| 37.14.4. DMA 模式           | 783 |

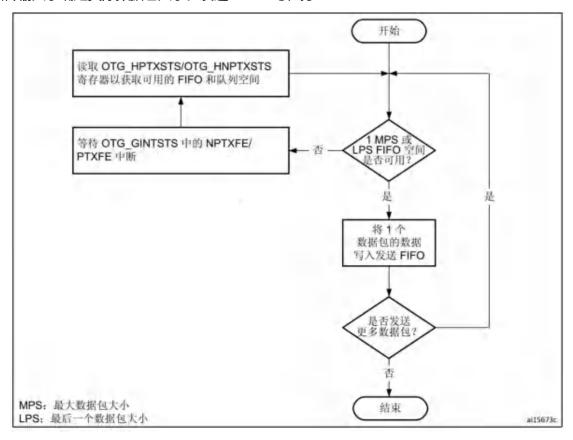

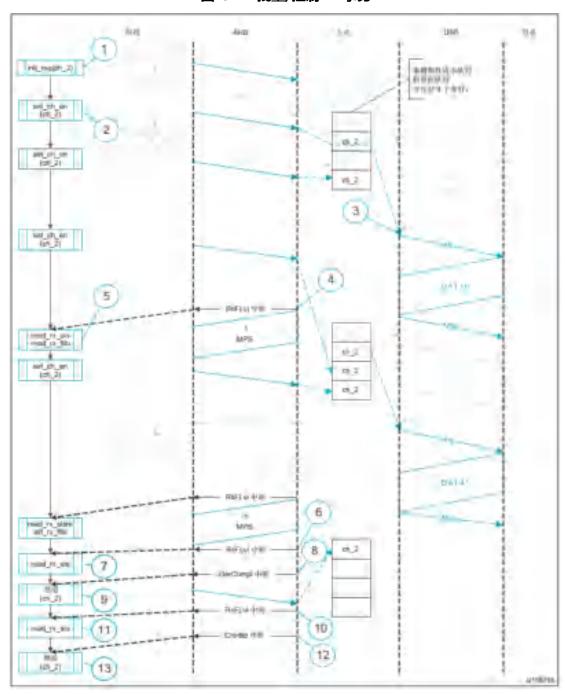

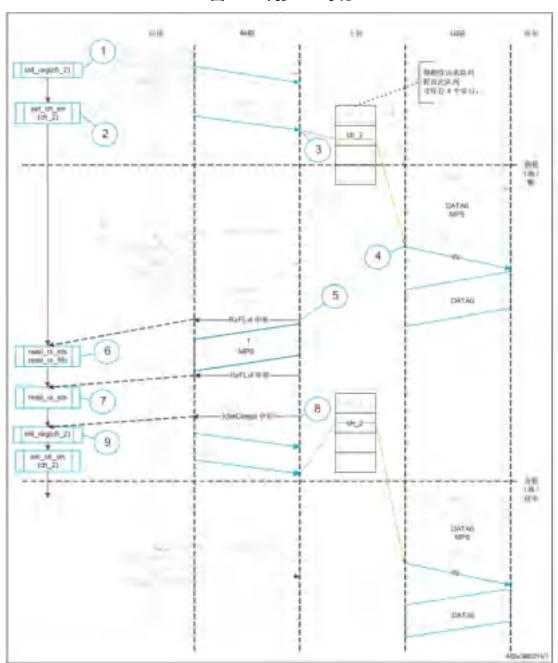

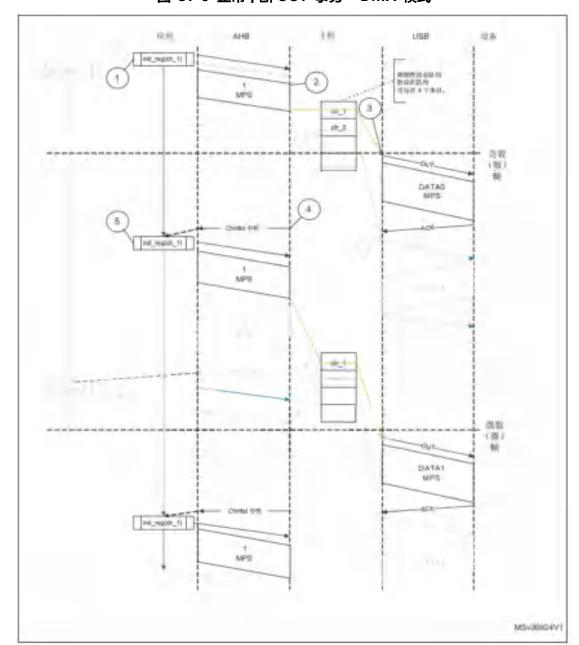

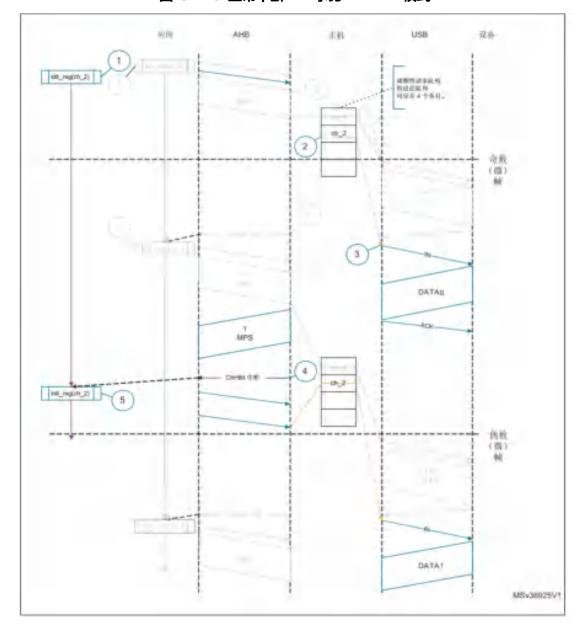

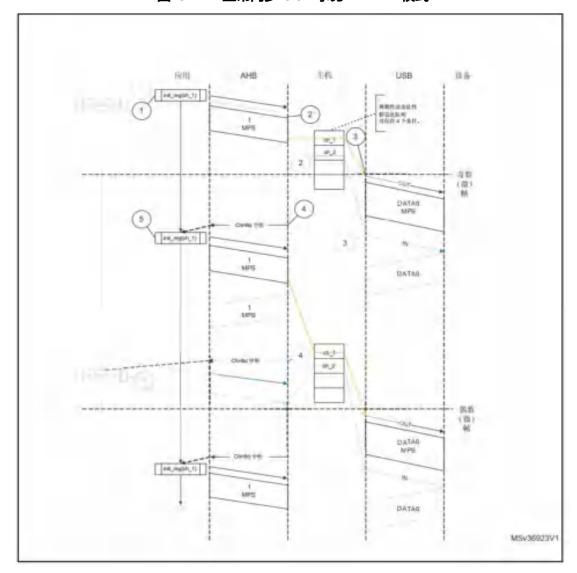

| 37.14.5. 主机编程模型           | 783 |

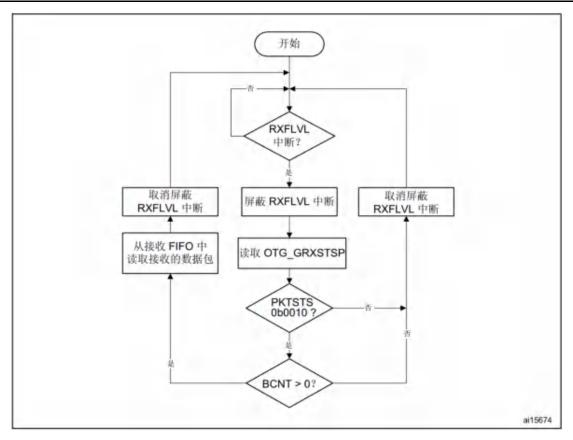

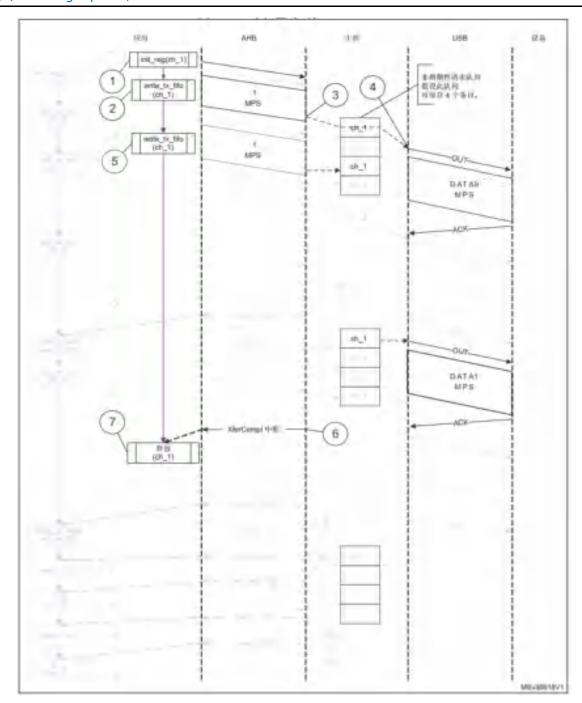

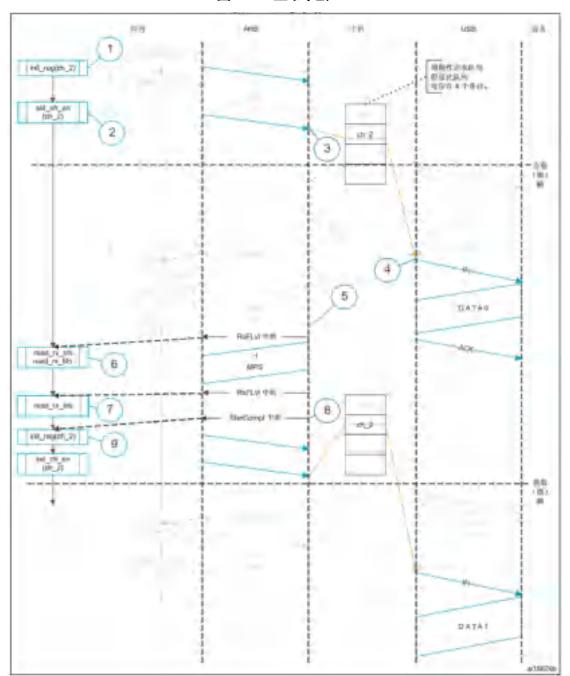

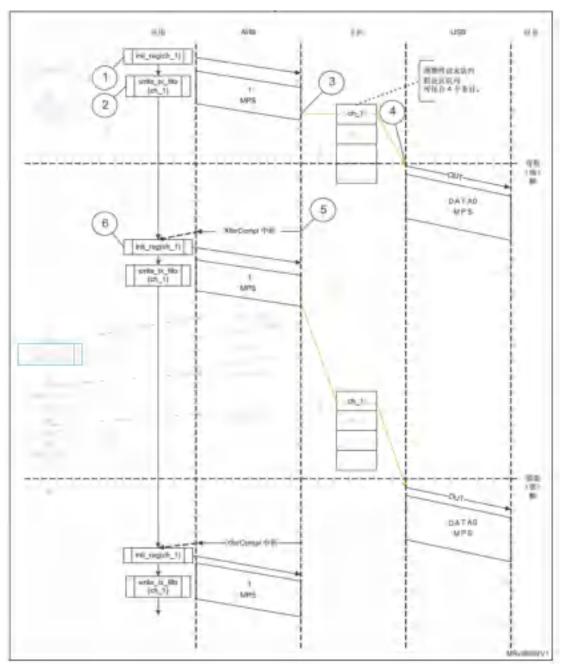

| 37.14.6. 设备编程模型           | 803 |

| 37.14.7. 最坏情况下的响应时间       | 818 |

| 37.14.8. OTG 编程模型         | 819 |

| 37.15. USB_OTH_HS 寄存器描述   | 823 |

| 37.15.1. 全局寄存器列表          | 824 |

| 37.15.2. 主机模式寄存器列表        | 863 |

| 37.15.3. 从机模式寄存器列表        | 876 |

| 37.15.4. 电源和时钟门控控制寄存器列表   | 910 |

| 38. 以太网 MAC 控制器 (ETH)     | 912 |

| 38.1. 概术                  | 912 |

| 38.2. 主 <del>要特</del> 性                 | 912            |

|-----------------------------------------|----------------|

| 38.2.1. MAC 内核特性                        | 912            |

| 38.2.2. DMA 特性                          | 913            |

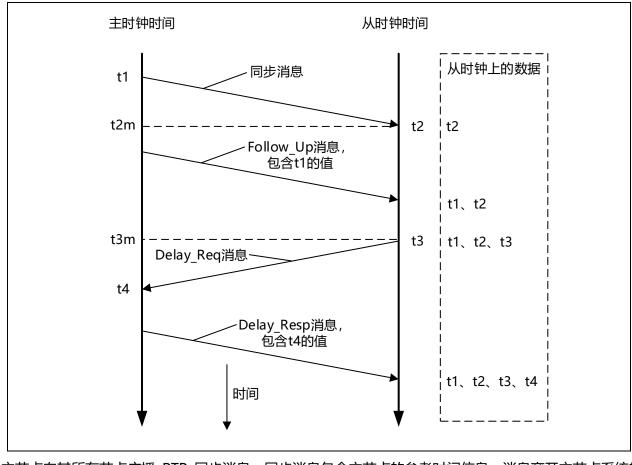

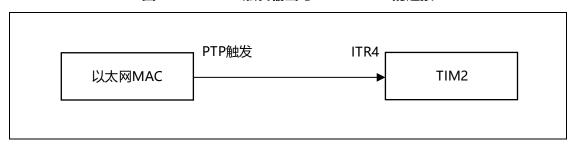

| 38.2.3. PTP 特性                          | 914            |

| 38.2.4. 总线接口特性                          | 914            |

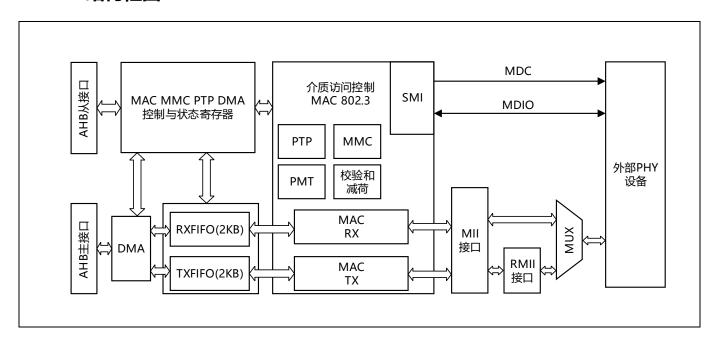

| 38.3. 功能描述                              | 915            |

| 38.3.1. 结构框图                            | 915            |

| 38.3.2. 以太网引脚                           | 915            |

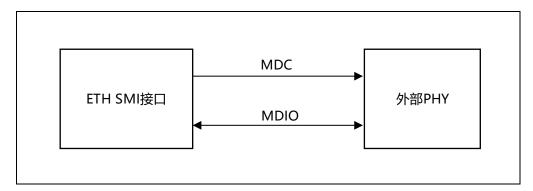

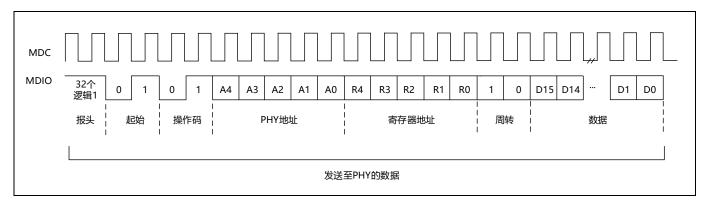

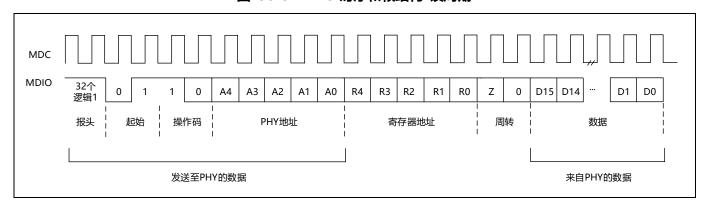

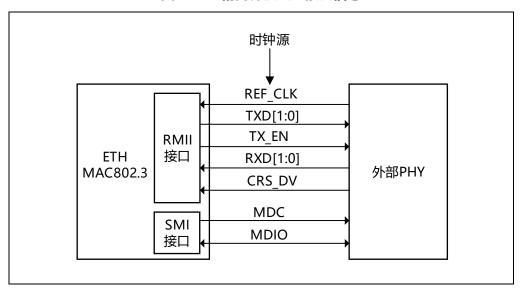

| 38.3.3. 以太网功能说明: SMI、MII 和 RMII         | 916            |

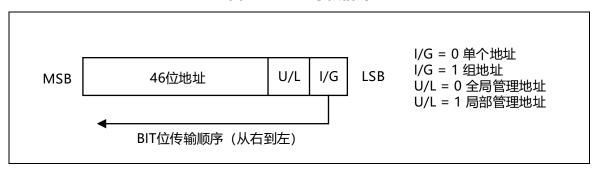

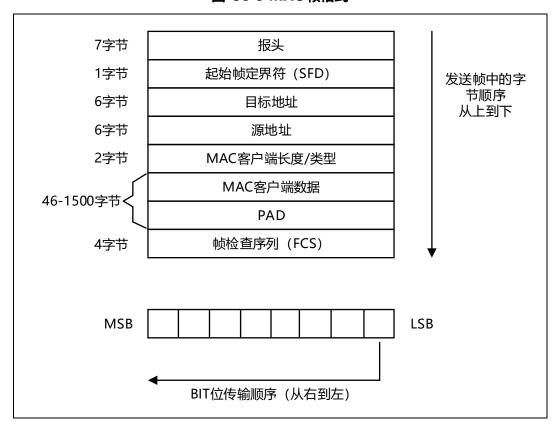

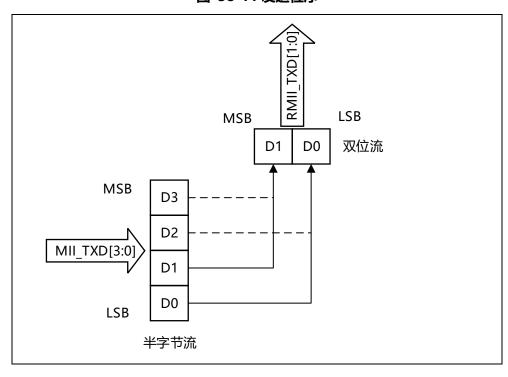

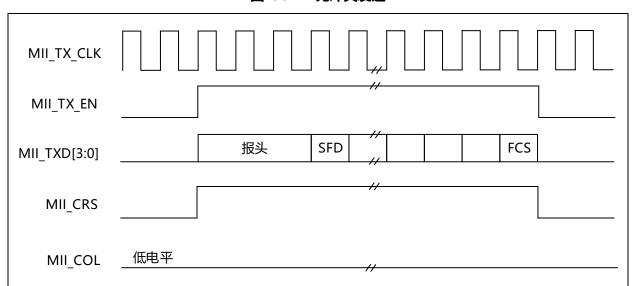

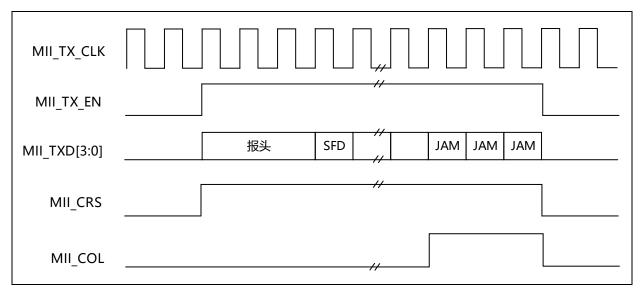

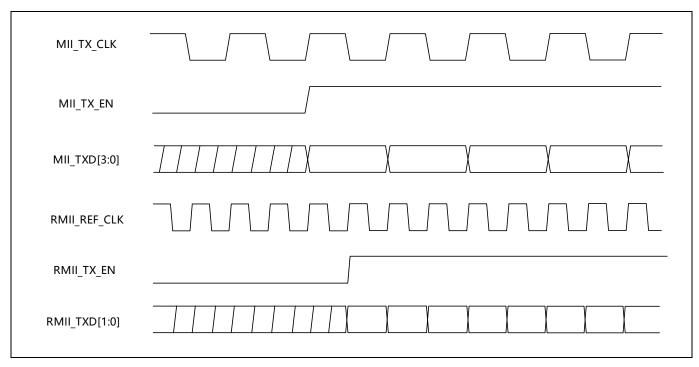

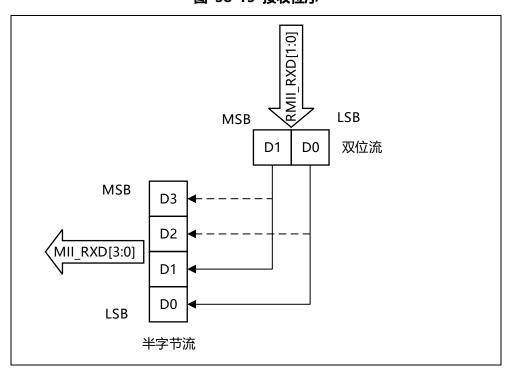

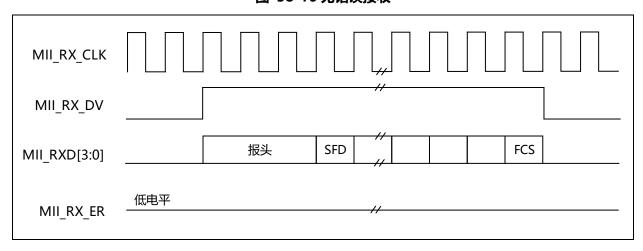

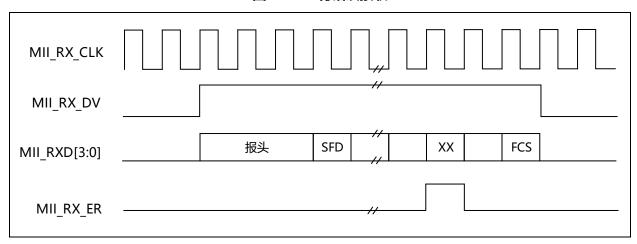

| 38.3.4. 以太网功能说明: MAC 802.3              | 921            |

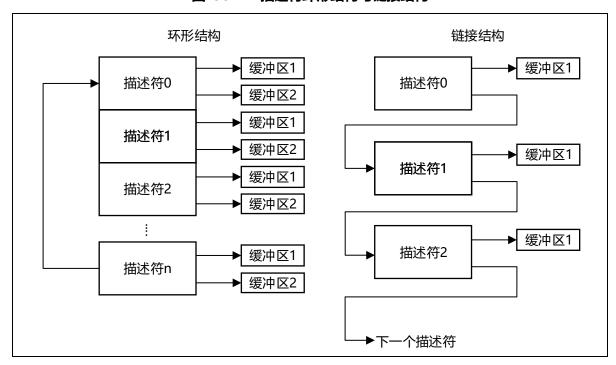

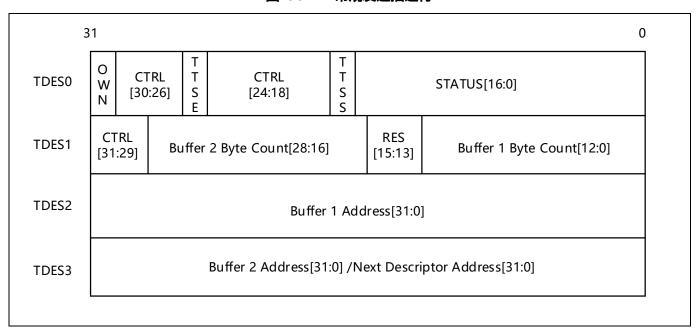

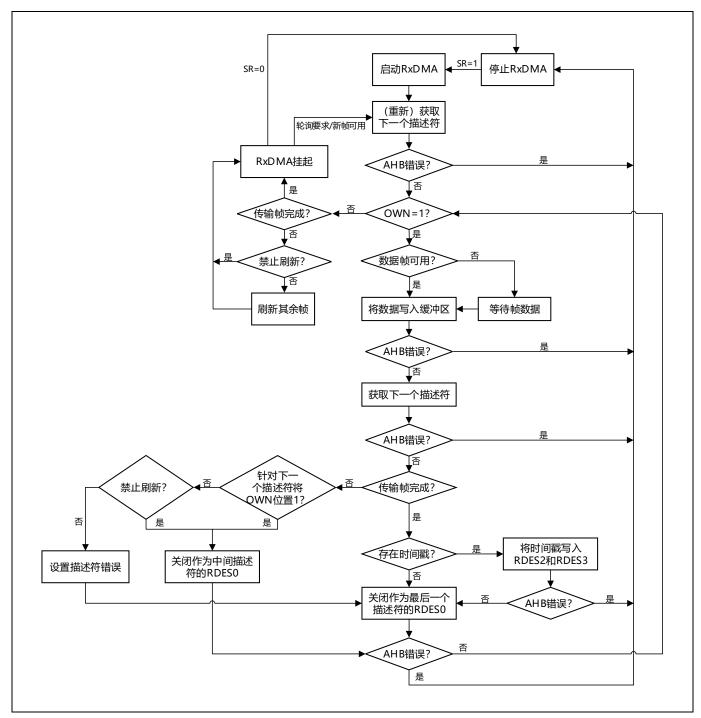

| 38.3.5. 以太网功能说明:DMA 控制器操作               | 945            |

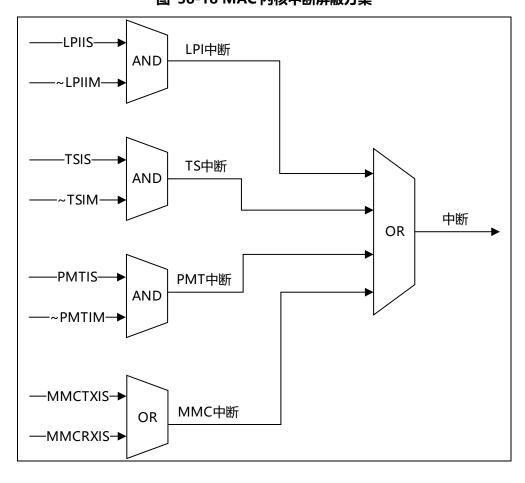

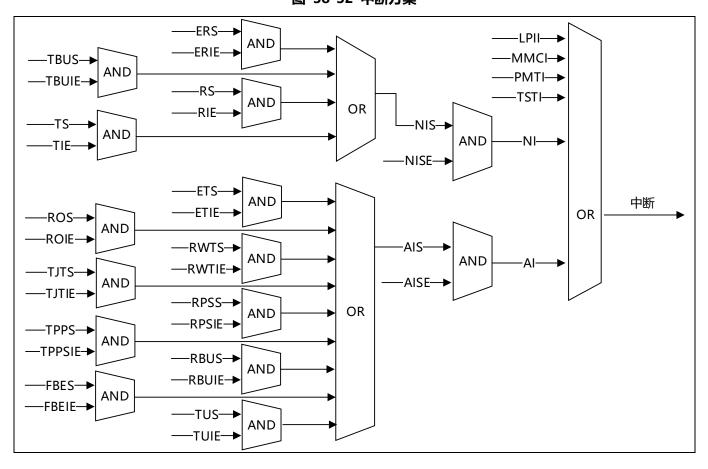

| 38.3.6. 以太网中断                           | 967            |

| 38.4. ETH 寄存器描述                         | 969            |

| 38.4.1. 寄存器列表                           | 969            |

| 38.4.2. MAC 配置寄存器(ETH_MACCR: 00h)       | 972            |

| 38.4.3. MAC 帧过滤寄存器(ETH_MACFFR: 04h)     | 975            |

| 38.4.4. MAC 散列表高位寄存器(ETH_MACHTHR: 0     | 976 (8h)       |

| 38.4.5. MAC 散列表低位寄存器(ETH_MACHTLR: 0     | Ch)977         |

| 38.4.6. MAC MII 地址寄存器(ETH_MACMIIAR: 10h | 1)977          |

| 38.4.7. MAC MII 数据寄存器(ETH_MACMIIDR: 14h | າ)978          |

| 38.4.8. MAC 流控制寄存器(ETH_MACFCR: 18h)     | 979            |

| 38.4.9. MAC VLAN 标记寄存器(ETH_MACVLANTR    | է: 1Ch)979     |

| 38.4.10. MAC 调试寄存器(ETH_MACDBGR: 24h)    | 980            |

| 38.4.11. MAC 远程唤醒帧过滤寄存器(ETH_MACRV       | VUFF: 28h)982  |

| 38.4.12. MAC PMT 控制和状态寄存器(ETH_MACP      | MTCSR: 2Ch)982 |

| 38.4.13. MAC LPI 控制和状态寄存器(ETH_MACLPI    | CSR: 30h) 983  |

| 38.4.14. MAC LPI 定时器控制寄存器(ETH_MACLPI    | TCR: 34h)984   |

| 38.4.15. MAC 中断状态寄存器(ETH_MACISR: 38h)   | 985            |

| 38.4.16. MAC 中断屏蔽寄存器(ETH_MACIMR: 3Ch    | ı)985          |

| 38.4.17. MAC 地址 0 高位寄存器(ETH_MACA0HR:    | 40h)986        |

| 38.4.18. MAC 地址 0 低位寄存器(ETH_MACA0LR: 4  | 44h)986        |

| 38.4.19. MAC 地址 1 高位寄存器(ETH_MACA1HR:    | 48h)987        |

| 38.4.20. MAC 地址 1 低位寄存器(ETH_MACA1LR: 4  | 4Ch)987        |

| 38.4.21. MAC 地址 2 高位寄存器(ETH_MACA2HR:    | 50h)987        |

| 38.4.22. MAC 地址 2 低位寄存器(ETH_MACA2LR:    | 54h)988        |

| 38.4.23. MAC 地址 3 高位寄存器(ETH_MACA3HR:    | 58h)988        |

| 38.4.24. MAC 地址 3 低位寄存器(ETH_MACA3LR:    | 5Ch) 989       |

| 38.4.25. MAC 看门狗超时寄存器(ETH_MACWTR: DCh)                | 989  |

|-------------------------------------------------------|------|

| 38.4.26. MMC 控制寄存器(ETH_MMCCR: 100h)                   | 990  |

| 38.4.27. MMC 接收中断寄存器(ETH_MMCRIR: 104h)                | 990  |

| 38.4.28. MMC 发送中断寄存器(ETH_MMCTIR: 108h)                | 991  |

| 38.4.29. MMC 接收中断屏蔽寄存器(ETH_MMCRIMR: 10Ch)             | 992  |

| 38.4.30. MMC 发送中断屏蔽寄存器(ETH_MMCTIMR: 110h)             | 992  |

| 38.4.31. MMC 在单个冲突后发送的良好帧计数器寄存器(ETH_MMCTGFSCCR: 14Ch) | 993  |

| 38.4.32. MMC 在多个冲突后发送的良好帧计数器寄存器(ETH_MMCTGFMCCR: 150h) | 993  |

| 38.4.33. MMC 发送的良好帧计数器寄存器(ETH_MMCTGFCR: 168h)         | 993  |

| 38.4.34. MMC 接收带有 CRC 错误帧计数器寄存器(ETH_MMCRFCECR: 194h)  | 993  |

| 38.4.35. MMC 接收带有对齐错误帧计数器寄存器(ETH_MMCRFAECR: 198h)     | 994  |

| 38.4.36. MMC 接收的良好单播帧计数器寄存器(ETH_MMCRGUFCR: 1C4h)      | 994  |

| 38.4.37. MAC L3 和 L4 控制 0 寄存器(ETH_MACL3L4C0R: 400h)   | 994  |

| 38.4.38. MAC L4 地址过滤器 0 寄存器(ETH_MACL4A0R: 404h)       | 996  |

| 38.4.39. MAC L3 地址 0 过滤器 0 寄存器(ETH_MACL3A00R: 410h)   | 996  |

| 38.4.40. MAC L3 地址 1 过滤器 0 寄存器(ETH_MACL3A10R: 414h)   | 997  |

| 38.4.41. MAC L3 地址 2 过滤器 0 寄存器(ETH_MACL3A20R: 418h)   | 997  |

| 38.4.42. MAC L3 地址 3 过滤器 0 寄存器(ETH_MACL3A30R: 41Ch)   | 997  |

| 38.4.43. MAC L3 和 L4 控制 1 寄存器(ETH_MACL3L4C1R: 430h)   | 997  |

| 38.4.44. MAC L4 地址过滤器 1 寄存器(ETH_MACL4A1R: 434h)       | 999  |

| 38.4.45. MAC L3 地址 0 过滤器 1 寄存器(ETH_MACL3A01R: 440h)   | 1000 |

| 38.4.46. MAC L3 地址 1 过滤器 1 寄存器(ETH_MACL3A11R: 444h)   | 1000 |

| 38.4.47. MAC L3 地址 2 过滤器 1 寄存器(ETH_MACL3A21R: 448h)   | 1000 |

| 38.4.48. MAC L3 地址 3 过滤器 1 寄存器(ETH_MACL3A31R: 44Ch)   | 1001 |

| 38.4.49. MAC VLAN 标记包含或替换寄存器(ETH_MACVTIRR: 584h)      | 1001 |

| 38.4.50. MAC VLAN 散列表寄存器(ETH_MACVHTR: 588h)           | 1002 |

| 38.4.51. PTP 时间戳控制寄存器(ETH_PTPTSCR: 700h)              | 1002 |

| 38.4.52. PTP 亚秒递增寄存器(ETH_PTPSSIR: 704h)               | 1005 |

| 38.4.53. PTP 时间戳高位寄存器(ETH_PTPTSHR: 708h)              | 1005 |

| 38.4.54. PTP 时间戳低位寄存器(ETH_PTPTSLR: 70Ch)              | 1005 |

| 38.4.55. PTP 时间戳高位更新寄存器(ETH_PTPTSHUR: 710h)           | 1006 |

| 38.4.56. PTP 时间戳低位更新寄存器(ETH_PTPTSLUR: 714h)           | 1006 |

| 38.4.57. PTP 时间戳加数寄存器(ETH_PTPTSAR: 718h)              | 1006 |

| 38.4.58. PTP 目标时间高位寄存器(ETH_PTPTTHR: 71Ch)             | 1006 |

| 38.4.59. PTP 目标时间低位寄存器(ETH_PTPTTLR: 720h)             | 1006 |

| 38.4.60. PTP 时间戳状态寄存器(ETH_PTPTSSR: 728h)              | 1007 |

| 38.4.61. PTP PPS 控制寄存器(ETH PTPPPSCR: 72Ch)            | 1008 |

版本: V1.5

|     | 38.4.62. PTP 辅助时间戳纳秒寄存器(ETH_PTPATSNR: 730h)        | 1010 |

|-----|----------------------------------------------------|------|

|     | 38.4.63. PTP 辅助时间戳秒寄存器(ETH_PTPATSSR: 734h)         | 1010 |

|     | 38.4.64. PTP PPS 间隔寄存器(ETH_PTPPPSIR: 760h)         | 1011 |

|     | 38.4.65. PTP PPS 宽度寄存器(ETH_PTPPPSWR: 764h)         | 1011 |

|     | 38.4.66. DMA 总线模式寄存器(ETH_DMABMR: 1000h)            | 1011 |

|     | 38.4.67. DMA 发送轮询要求寄存器(ETH_DMATPDR: 1004h)         | 1013 |

|     | 38.4.68. DMA 接收轮询要求寄存器(ETH_DMARPDR: 1008h)         | 1013 |

|     | 38.4.69. DMA 接收描述符列表地址寄存器(ETH_DMARDLAR: 100Ch)     | 1014 |

|     | 38.4.70. DMA 发送描述符列表地址寄存器(ETH_DMATDLAR: 1010h)     | 1014 |

|     | 38.4.71. DMA 状态寄存器(ETH_DMASR: 1014h)               | 1014 |

|     | 38.4.72. DMA 工作模式寄存器(ETH_DMAOMR: 1018h)            | 1017 |

|     | 38.4.73. DMA 中断使能寄存器(ETH_DMAIER: 101Ch)            | 1020 |

|     | 38.4.74. DMA 丢失帧和缓冲区上溢计数器寄存器(ETH_DMAMFBOCR: 1020h) | 1022 |

|     | 38.4.75. DMA 接收中断看门狗定时器寄存器(ETH_DMARIWTR: 1024h)    | 1022 |

|     | 38.4.76. DMA 当前主机发送描述符寄存器(ETH_DMACHTDR: 1048h)     | 1022 |

|     | 38.4.77. DMA 当前主机接收描述符寄存器(ETH_DMACHRDR: 104Ch)     | 1023 |

|     | 38.4.78. DMA 当前主机发送缓冲区地址寄存器(ETH_DMACHTBAR: 1050h)  | 1023 |

|     | 38.4.79. DMA 当前主机接收缓冲区地址寄存器(ETH_DMACHRBAR: 1054h)  | 1023 |

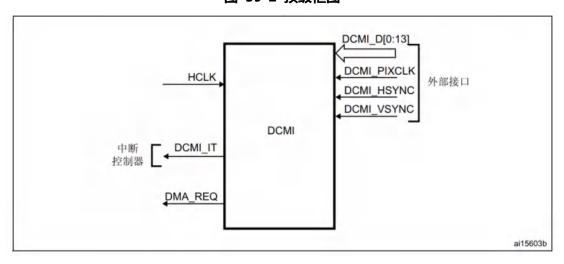

| 39. | 数字摄像头接口 (DCMI)                                     | 1024 |

|     | 39.1. 概述                                           | 1024 |

|     | 39.2. 主要特性                                         | 1024 |

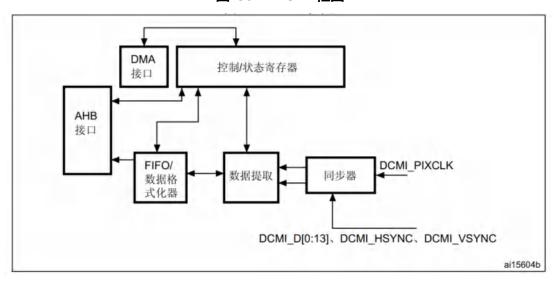

|     | 39.3. 功能描述                                         | 1024 |

|     | 39.3.1. 结构框图                                       | 1025 |

|     | 39.3.2. DCMI 时钟                                    | 1025 |

|     | 39.3.3. DMA 接口                                     |      |

|     | 39.3.4. DCMI 物理接口                                  | 1025 |

|     | 39.3.5. 同步                                         | 1027 |

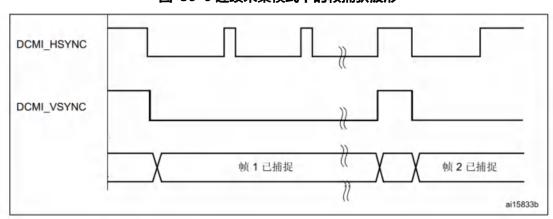

|     | 39.3.6. 捕获模式                                       | 1029 |

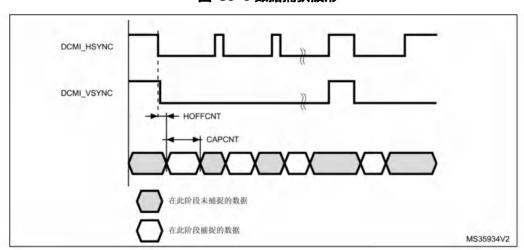

|     | 39.3.7. 裁剪功能                                       | 1030 |

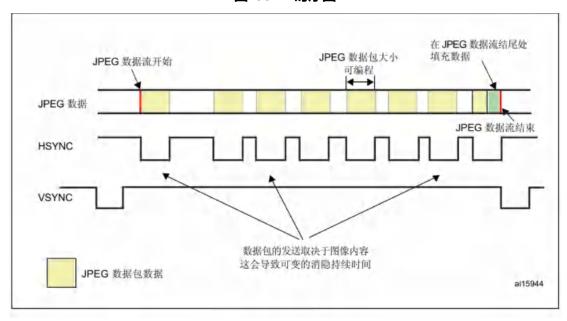

|     | 39.3.8. JPEG 格式                                    | 1031 |

|     | 39.4. 数据格式说明                                       | 1031 |

|     | 39.4.1. 数据格式                                       | 1031 |

|     | 39.4.2. 单色格式                                       | 1032 |

|     | 39.4.3. RGB 格式                                     |      |

|     | 39.4.4. YCbCr 格式                                   |      |

|     | 39.4.5. YCbCr 格式-仅含 Y 分量                           | 1033 |

|     | 39.5. 信号描述                                         | 1033 |

| 39.6. DCMI 中断                        | 1034 |

|--------------------------------------|------|

| 39.7. DCMI 寄存器描述                     | 1035 |

| 39.7.1. 寄存器列表                        | 1035 |

| 39.7.2. 模式寄存器(DCMI_CR: 00h)          | 1035 |

| 39.7.3. 控制寄存器(DCMI_SR: 04h)          | 1037 |

| 39.7.4. 原始中断状态寄存器(DCMI_RIS: 08h)     | 1037 |

| 39.7.5. 中断使能寄存器(DCMI_IER: 0Ch)       | 1038 |

| 39.7.6. 屏蔽中断状态寄存器(DCMI_MIS: 10h)     | 1039 |

| 39.7.7. 中断清零寄存器(DCMI_ICR: 14h)       | 1039 |

| 39.7.8. 内嵌同步码寄存器(DCMI_ESCR: 18h)     | 1040 |

| 39.7.9. 内嵌同步码寄存器(DCMI_ESUR: 1Ch)     | 1040 |

| 39.7.10. 裁剪窗口起点寄存器(DCMI_CWSTRT: 20h) | 1041 |

| 39.7.11. 裁剪大小寄存器(DCMI_CWSIZE: 24h)   | 1041 |

| 39.7.12. 数据寄存器(DCMI_DR: 28h)         | 1042 |

| 40. LCD-TFT 控制器 (LTDC)               | 1043 |

| 40.1. 概述                             | 1043 |

| 40.2. 主要特性                           | 1043 |

| 40.3. 功能描述                           | 1044 |

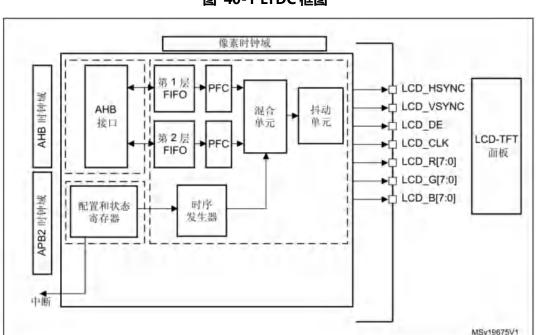

| 40.3.1. LTDC 框图                      | 1044 |

| 40.3.2. LTDC 复位和时钟                   | 1044 |

| 40.3.3. LCDC 引脚和信号接口                 | 1045 |

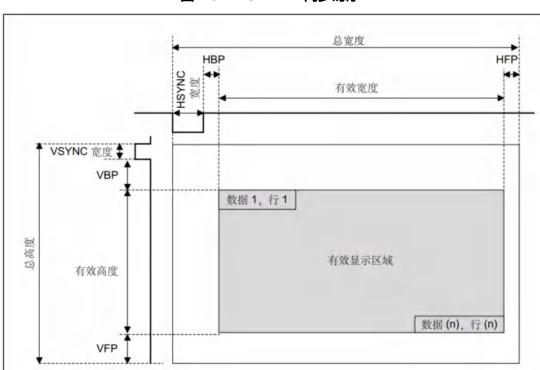

| 40.4. LTDC 可编程参数                     | 1045 |

| 40.4.1. LTDC 全局配置参数                  | 1045 |

| 40.5. LTDC 中断                        | 1051 |

| 40.6. 配置流程                           | 1051 |

| 40.7. LTDC 寄存器描述                     | 1052 |

| 40.7.1. 寄存器列表                        | 1052 |

| 40.7.2. 同步大小配置寄存器(LTDC_SSCR: 08h)    | 1053 |

| 40.7.3. 后沿配置寄存器(LTDC_BPCR: 0Ch)      | 1054 |

| 40.7.4. 有效宽度配置寄存器(LTDC_AWCR: 10h)    | 1054 |

| 40.7.5. 总宽度配置寄存器(LTDC_TWCR: 14h)     | 1054 |

| 40.7.6. 总宽度配置寄存器(LTDC_GCR: 18h)      | 1055 |

| 40.7.7. 影子重载配置寄存器(LTDC_SRCR: 24h)    | 1056 |

| 40.7.8. 背景色配置寄存器(LTDC_BCCR: 2Ch)     | 1056 |

| 40.7.9. 中断使能寄存器(LTDC_IER: 34h)       | 1056 |

| 40.7.10. 中断状态寄存器(LTDC_ISR: 38h)      | 1057 |

| 40.7.11. 中断清零寄存器(LTDC_ICR: 3Ch)      | 1057 |

| 40.7.12. 行中断位置配置寄存器(LTDC_LIPCR: 40h)            | 1057 |

|-------------------------------------------------|------|

| 40.7.13. 当前位置状态寄存器(LTDC_CPSR: 44h)              | 1057 |

| 40.7.14. 当前显示状态寄存器(LTDC_CDSR: 48h)              | 1058 |

| 40.7.15. 第 1 层控制寄存器(LTDC_L1CR: 84h)             | 1058 |

| 40.7.16. 第 1 层水平位置配置寄存器(LTDC_L1WHPCR: 88h)      | 1059 |

| 40.7.17. 第 1 层垂直位置配置寄存器(LTDC_L1WVPCR: 8Ch)      | 1059 |

| 40.7.18. 第 1 层色键配置寄存器(LTDC_L1CKCR: 90h)         | 1059 |

| 40.7.19. 第 1 层像素格式配置寄存器(LTDC_L1PFCR: 94h)       | 1059 |

| 40.7.20. 第 1 层常数 Alpha 配置寄存器(LTDC_L1CACR: 98h)  | 1060 |

| 40.7.21. 第 1 层默认颜色配置寄存器(LTDC_L1DCCR: 9Ch)       | 1060 |

| 40.7.22. 第 1 层混合系数配置寄存器(LTDC_L1BFCR: A0h)       | 1060 |

| 40.7.23. 第 1 层颜色帧缓冲区地址寄存器(LTDC_L1CFBAR: ACh)    | 1061 |

| 40.7.24. 第 1 层颜色帧缓冲区长度寄存器(LTDC_L1CFBLR: B0h)    | 1061 |

| 40.7.25. 第 1 层颜色帧缓冲区行数寄存器(LTDC_L1CFBLNR: B4h)   | 1062 |

| 40.7.26. 第 1 层 CLUT 写寄存器(LTDC_L1CLUTWR : C4h)   | 1062 |

| 40.7.27. 第 2 层控制寄存器(LTDC_L2CR: 104h)            | 1062 |

| 40.7.28. 第 2 层水平位置配置寄存器(LTDC_L2WHPCR: 108h)     | 1063 |

| 40.7.29. 第 2 层垂直位置配置寄存器(LTDC_L2WVPCR: 10Ch)     | 1063 |

| 40.7.30. 第 2 层色键配置寄存器(LTDC_L2CKCR: 110h)        | 1063 |

| 40.7.31. 第 2 层像素格式配置寄存器(LTDC_L2PFCR: 114h)      | 1064 |

| 40.7.32. 第 2 层常数 Alpha 配置寄存器(LTDC_L2CACR: 118h) | 1064 |

| 40.7.33. 第 2 层默认颜色配置寄存器(LTDC_L2DCCR: 11Ch)      | 1064 |

| 40.7.34. 第 2 层混合系数配置寄存器(LTDC_L2BFCR: 120h)      | 1064 |

| 40.7.35. 第 2 层颜色帧缓冲区地址寄存器(LTDC_L2CFBAR: 12Ch)   | 1065 |

| 40.7.36. 第 2 层颜色帧缓冲区长度寄存器(LTDC_L2CFBLR: 130h)   | 1065 |

| 40.7.37. 第 2 层颜色帧缓冲区行数寄存器(LTDC_L2CFBLNR: 134h)  | 1066 |

| 40.7.38. 第 2 层 CLUT 写寄存器(LTDC_L2CLUTWR: 144h)   | 1066 |

| 41. 图像加速器 (DMA2D)                               | 1067 |

| 41.1. 概述                                        | 1067 |

| 41.2. 主要特性                                      | 1067 |

| 41.3. 功能描述                                      | 1068 |

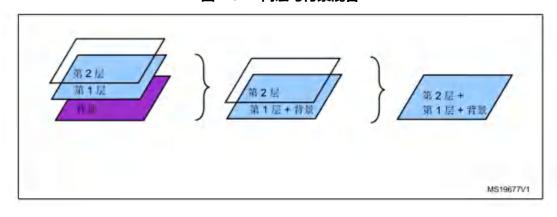

| 41.3.1. 功能概述                                    | 1068 |

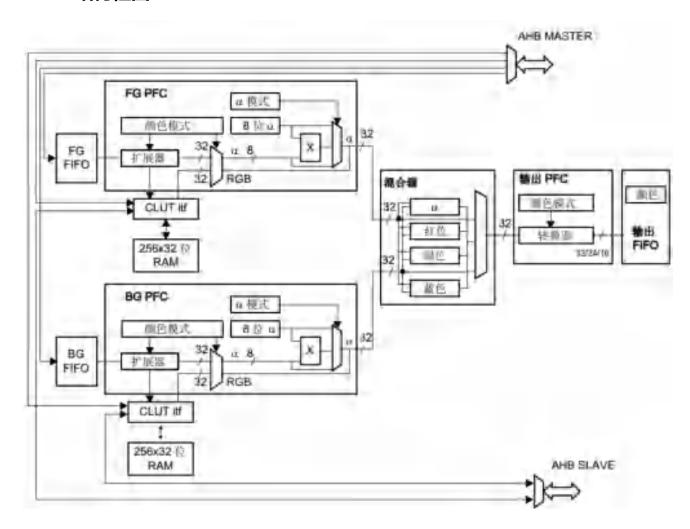

| 41.3.2. 结构框图                                    | 1068 |

| 41.3.3. DMA2D 控制                                | 1068 |

| 41.3.4. DMA2D 前景层 FIFO 和背景层 FIFO                | 1069 |

| 41.3.5. DMA2D 前景层和背景层像素格式转换器 (PFC)              | 1069 |

| 41.3.6. DMA2D 前景层 FIFO 和背景层 CLUT 接口             | 1071 |

|     | 41.3.7. DMA2D 混合器                                 | 1072 |

|-----|---------------------------------------------------|------|

|     | 41.3.8. DMA2D 输出 PFC                              | 1072 |

|     | 41.3.9. DMA2D 输出 FIFO                             | 1072 |

|     | 41.3.10. DMA2D AHB 主设备端口定时器                       | 1073 |

|     | 41.3.11. DMA2D 事务                                 | 1073 |

|     | 41.3.12. DMA2D 配置                                 | 1073 |

|     | 41.4. DMA2D 中断                                    | 1077 |

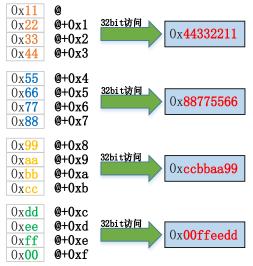

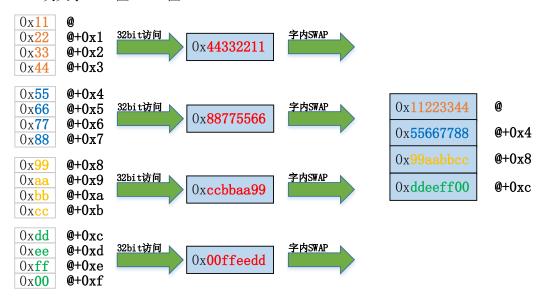

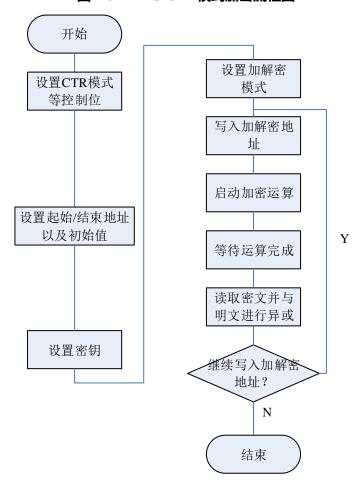

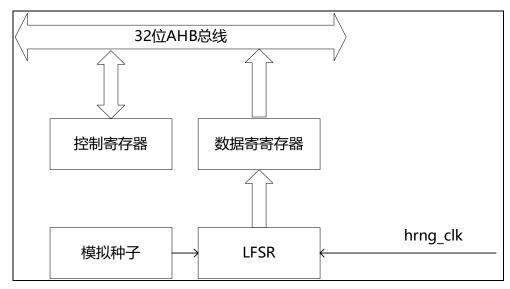

|     | 41.5. DMA2D 寄存器描述                                 | 1077 |